Hola amigos del foro, tengo un ejercicio de diseño de amplicador con un BJT, la duda es: a la hora de calcular la tensión en la resistencia del emisor, ¿cuál es la diferencia entre calcularla como VRE = Vcc - Vce - Vc y aplicar el criterio VRE = 0.1*Vcc?

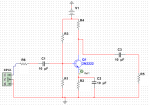

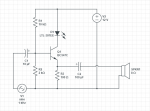

Este es el circuito en cuestión

Desde ya gracias y saludos

Este es el circuito en cuestión

Desde ya gracias y saludos