Foristas,

Creo este tema para empezar a documentar el desarrollo de mi proxima version de osciloscopio digital. Estimo que al ir tirando los avances aqui, puedo no solo compartirlo sino obtener muy buenas ideas.

Aclaracion importante: Es un proyecto en desarrollo y va mutando constantemente. Ya estoy cerca de pasar al diseño de PCB pero primero quiero dejar perfecto esto en la teoria.

Otra aclaracion: Con este osciloscopio se intenta obtener algo "decente", utilizando los materiales mas conseguibles que se pueda.

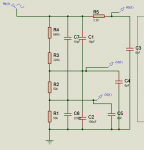

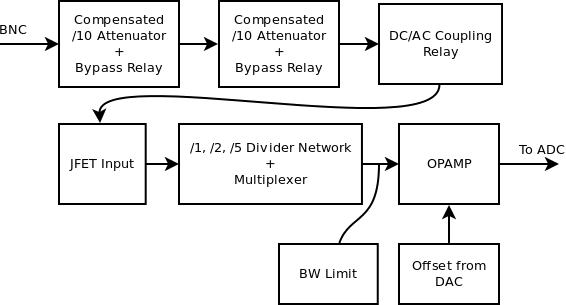

El esquematico que adjunto es una impresion de la simulacion de proteus de la etapa de captura digital, por lo tanto hay unas cuantas cosas que se han puesto alli solo a fines de simulacion. (ej: inversores, puerto serie rs232, generadores de señal, etc)

Tambien se intenta obtener unas cuantas partes desde el reciclaje de computadoras. Tooooodo este circuito podria implementarse en una FPGA y andaria a los tiros pero lamentablemente no las consigo y con la importacion se me hace prohibitivo. Sin embargo, los PLD estan ahi, ya veran.

El osciloscopio, si despierta interes, vendra con esquematicos, PCB y software (en visual basic .net, pero si alguien quiere colaborar con java o algo que ande en linux, puedo proporcionar toda la informacion del protocolo de comunicacion).

Enumero algunas de las caracteristicas principales:

- Tasa de captura digital de 80 MSPS, real time.

- 64 Kb de profundidad de memoria x canal, cantidad de datos pre-trigger seleccionables

- 2 canales + trigger externo

- Trigger de hardware digital, trigger externo analogico y trigger por software

- Ancho de banda analogico a definir, posiblemente alrededor de los 100mhz

- Conexion USB, alimentacion desde el USB (veremos si con 500ma me alcanza)

Componentes y su decision:

- 2 conversores ADC ADS831 de TI. Estos conversores los obtuve como samples y van a un maximo de 80MSPS. Entre estos y la ram daran en ultima instancia la velocidad.

y van a un maximo de 80MSPS. Entre estos y la ram daran en ultima instancia la velocidad.

- Modulo Oscilador de cristal de 80mhz rescatado de placas viejas de PC

- Transceivers 74LS245 rescatados de lectoras de CD y motherboard viejas. Necesarios para direccionar los datos. (podria usar el 74LS244 pero los pines son super incomodos para el PCB)

- 4 Memorias SRAM de 15ns 61256 rescatadas en este caso de un modulito de memoria cache de mother para 486, pero que tambien se obtienen de lectoras de CD viejas.

- Micro PIC 18F4550 (probablemente un 18F2550 ande OK pero habria que multiplexar pines)

- 74HC4094, serial shifter, simplemente para ahorrar pines

- flip flop 74F74 (importante la F) y NAND 74F00 rescatados, otra vez, de lectoras de CD y plaqueterio de PC. Estos cumplen la funcion de dividir la captura entre 2 grupos de RAM para asi poder alcanzar 80 MSPS con memorias de 15 nanos. (grabo en una ram en ciclo de reloj alto y en la otra en bajo). Este conjunto estoy evaluando reemplazarlo por una GAL

- Por ultimo, y super importante: GAL22v10 de 5ns de tiempo de propagacion (las mas rapidas que consegui). Simplemente porque las tengo para usarlas y se que esto es una complicacion muy grande para otra persona que quiera hacerlo.

La finalidad de este post NO es proveer un circuito para armar y usar. Eso es imposible dada la complejidad del mismo y la disponibilidad de componentes. La idea es brindar algo que funcione y que sirva de base para sus diseños propios basados en los componentes que tengan.

Por ej: Yo uso 3 GAL 22v10:

- 1r PLD es el trigger digital. Basicamente es un comparador de 2 palabras de 8 bits y tiene 1 pin de salida que dice si A > B. Esto se puede reemplazar por 1 integrado de la serie TTL que ahora no recuerdo la denominacion. Lo que pasa que ese integrado no es tan rapido como la GAL.

- 2do PLD es el contador SINCRONO (importantisimo) de 9 bits con carryout, reemplazable por 74F269 de la serie TTL

- 3r PLD cumple multiple funcion de:

a- contador sincrono de los bits restantes

b- selector de fuente de reloj

c- determinador de trigger

d- generador de clock para el contador de desborde (integrado en el PIC pufff 1 integrado menos!)

Este PLD es reemplazable por otro 74F269 y unas cuantas NAND + flip flops

Como ven, si bien esto asi como esta "no sirve para nada", si es una buena base de ideas si interpretan el esquematico. Voy a ir posteando a medida que avance el proyecto y espero sus ideas o preguntas!

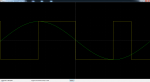

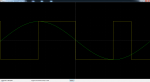

Aca les dejo una captura de pantalla para ir entusiasmando:

Se trata de una senoidal de 50khz en el canal A y una cuadrada de 100khz en canal B sampleadas a 50 MSPS (a 80mhz el proteus me pone impaciente )

)

En el programa, cada division tiene 100 puntos de sample.

A 80 mhz, este osciloscopio tendria su escala minima en 1.25us / DIV a 100 samples pero gracias al forista palurdo que me dio una leccion de matematicas, a partir de alli empieza la interpolacion y se lo puede hacer ver muy razonablemente señales en el dominio de los 200ns / DIV.

Ademas, estoy estudiando agregarle al menos 1 disparo retardado de trigger para hacer Equivalent time sampling pero no estoy seguro de querer complicar mas una PCB de por si complicada.

Proximamente, mas avances, sus opiniones, ideas, criticas, etc son bienvenidas!

Creo este tema para empezar a documentar el desarrollo de mi proxima version de osciloscopio digital. Estimo que al ir tirando los avances aqui, puedo no solo compartirlo sino obtener muy buenas ideas.

Aclaracion importante: Es un proyecto en desarrollo y va mutando constantemente. Ya estoy cerca de pasar al diseño de PCB pero primero quiero dejar perfecto esto en la teoria.

Otra aclaracion: Con este osciloscopio se intenta obtener algo "decente", utilizando los materiales mas conseguibles que se pueda.

El esquematico que adjunto es una impresion de la simulacion de proteus de la etapa de captura digital, por lo tanto hay unas cuantas cosas que se han puesto alli solo a fines de simulacion. (ej: inversores, puerto serie rs232, generadores de señal, etc)

Tambien se intenta obtener unas cuantas partes desde el reciclaje de computadoras. Tooooodo este circuito podria implementarse en una FPGA y andaria a los tiros pero lamentablemente no las consigo y con la importacion se me hace prohibitivo. Sin embargo, los PLD estan ahi, ya veran.

El osciloscopio, si despierta interes, vendra con esquematicos, PCB y software (en visual basic .net, pero si alguien quiere colaborar con java o algo que ande en linux, puedo proporcionar toda la informacion del protocolo de comunicacion).

Enumero algunas de las caracteristicas principales:

- Tasa de captura digital de 80 MSPS, real time.

- 64 Kb de profundidad de memoria x canal, cantidad de datos pre-trigger seleccionables

- 2 canales + trigger externo

- Trigger de hardware digital, trigger externo analogico y trigger por software

- Ancho de banda analogico a definir, posiblemente alrededor de los 100mhz

- Conexion USB, alimentacion desde el USB (veremos si con 500ma me alcanza)

Componentes y su decision:

- 2 conversores ADC ADS831 de TI. Estos conversores los obtuve como samples

- Modulo Oscilador de cristal de 80mhz rescatado de placas viejas de PC

- Transceivers 74LS245 rescatados de lectoras de CD y motherboard viejas. Necesarios para direccionar los datos. (podria usar el 74LS244 pero los pines son super incomodos para el PCB)

- 4 Memorias SRAM de 15ns 61256 rescatadas en este caso de un modulito de memoria cache de mother para 486, pero que tambien se obtienen de lectoras de CD viejas.

- Micro PIC 18F4550 (probablemente un 18F2550 ande OK pero habria que multiplexar pines)

- 74HC4094, serial shifter, simplemente para ahorrar pines

- flip flop 74F74 (importante la F) y NAND 74F00 rescatados, otra vez, de lectoras de CD y plaqueterio de PC. Estos cumplen la funcion de dividir la captura entre 2 grupos de RAM para asi poder alcanzar 80 MSPS con memorias de 15 nanos. (grabo en una ram en ciclo de reloj alto y en la otra en bajo). Este conjunto estoy evaluando reemplazarlo por una GAL

- Por ultimo, y super importante: GAL22v10 de 5ns de tiempo de propagacion (las mas rapidas que consegui). Simplemente porque las tengo para usarlas y se que esto es una complicacion muy grande para otra persona que quiera hacerlo.

La finalidad de este post NO es proveer un circuito para armar y usar. Eso es imposible dada la complejidad del mismo y la disponibilidad de componentes. La idea es brindar algo que funcione y que sirva de base para sus diseños propios basados en los componentes que tengan.

Por ej: Yo uso 3 GAL 22v10:

- 1r PLD es el trigger digital. Basicamente es un comparador de 2 palabras de 8 bits y tiene 1 pin de salida que dice si A > B. Esto se puede reemplazar por 1 integrado de la serie TTL que ahora no recuerdo la denominacion. Lo que pasa que ese integrado no es tan rapido como la GAL.

- 2do PLD es el contador SINCRONO (importantisimo) de 9 bits con carryout, reemplazable por 74F269 de la serie TTL

- 3r PLD cumple multiple funcion de:

a- contador sincrono de los bits restantes

b- selector de fuente de reloj

c- determinador de trigger

d- generador de clock para el contador de desborde (integrado en el PIC pufff 1 integrado menos!)

Este PLD es reemplazable por otro 74F269 y unas cuantas NAND + flip flops

Como ven, si bien esto asi como esta "no sirve para nada", si es una buena base de ideas si interpretan el esquematico. Voy a ir posteando a medida que avance el proyecto y espero sus ideas o preguntas!

Aca les dejo una captura de pantalla para ir entusiasmando:

Se trata de una senoidal de 50khz en el canal A y una cuadrada de 100khz en canal B sampleadas a 50 MSPS (a 80mhz el proteus me pone impaciente

En el programa, cada division tiene 100 puntos de sample.

A 80 mhz, este osciloscopio tendria su escala minima en 1.25us / DIV a 100 samples pero gracias al forista palurdo que me dio una leccion de matematicas, a partir de alli empieza la interpolacion y se lo puede hacer ver muy razonablemente señales en el dominio de los 200ns / DIV.

Ademas, estoy estudiando agregarle al menos 1 disparo retardado de trigger para hacer Equivalent time sampling pero no estoy seguro de querer complicar mas una PCB de por si complicada.

Proximamente, mas avances, sus opiniones, ideas, criticas, etc son bienvenidas!