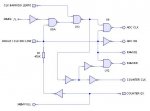

Hice un circuito que graba datos en una memoria SRAM de 15ns de 32KB (15 lineas de direccion)

Dispongo solamente informacion de contadores 4040 de 12bits, los intente poner en cascada conectando el Q11 del primero con el CLOCK del segundo, mientras que ese Q11 tambien va a A11 de la memoria, y el Q0 del segundo contador al Q12 de la memoria.

El dato que le grabo para prueba es 128.

Encuentro problemas, a partir de el dato nro: 16032 la memoria graba (o entrega para lectura) basura, 8 valores ~255, luego 16 valores ~0, luego 16 valores ~255 y asi 16 y 16 hasta los 32KB. Extrañamente LOGICO (por el numero) y constante el error, no aleatorio.

Aun no encuentro la fuente del problema (si alguien tiene pistas de como encontrar el problema para proporcionar, mucho mejor)

La pregunta principal es si alguien conoce una referencia de integrado contador binario 8 bits, medianamente conseguible en cordoba-argentina. El mismo debe poder soportar una frecuencia de 20mhz. (por mas que he buscado no consigo referencias, y una referencia que vi en internet no la consigo en el pais) y debe ser "cascadeable"

Otra pregunta: Esta bien la forma de ponerlos en cascada que hice? Segun proteus si, aunque este integrado no tenga un Q~ especifico para eso

Y por ultimo, lo que dije arriba, si alguien sabe por donde puede estar viniendo mi problema y me puede ayudar, mejor. Revise el PCB y no hay cortos entre pistas (aunque muchas estan demasiado cerca o pasan entre pines de integrado, creando quiza capacitancias que no pueden ser medidas con capacimetro)

Dispongo solamente informacion de contadores 4040 de 12bits, los intente poner en cascada conectando el Q11 del primero con el CLOCK del segundo, mientras que ese Q11 tambien va a A11 de la memoria, y el Q0 del segundo contador al Q12 de la memoria.

El dato que le grabo para prueba es 128.

Encuentro problemas, a partir de el dato nro: 16032 la memoria graba (o entrega para lectura) basura, 8 valores ~255, luego 16 valores ~0, luego 16 valores ~255 y asi 16 y 16 hasta los 32KB. Extrañamente LOGICO (por el numero) y constante el error, no aleatorio.

Aun no encuentro la fuente del problema (si alguien tiene pistas de como encontrar el problema para proporcionar, mucho mejor)

La pregunta principal es si alguien conoce una referencia de integrado contador binario 8 bits, medianamente conseguible en cordoba-argentina. El mismo debe poder soportar una frecuencia de 20mhz. (por mas que he buscado no consigo referencias, y una referencia que vi en internet no la consigo en el pais) y debe ser "cascadeable"

Otra pregunta: Esta bien la forma de ponerlos en cascada que hice? Segun proteus si, aunque este integrado no tenga un Q~ especifico para eso

Y por ultimo, lo que dije arriba, si alguien sabe por donde puede estar viniendo mi problema y me puede ayudar, mejor. Revise el PCB y no hay cortos entre pistas (aunque muchas estan demasiado cerca o pasan entre pines de integrado, creando quiza capacitancias que no pueden ser medidas con capacimetro)

Última edición: