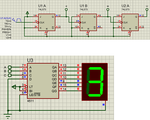

Saludos camaradas. Hace unos dias he comenzado con el diseño de un contador usando como base 3 flip-flops del tipo JK en configuracion asincrona tal como se ve en la imagen. En base a eso el objetivo final es accionar un display de 7 segmentos del tipo catodo comun. De allí viene mi duda, si es que requiero utilizar un decodificador BCD a 7 segmentos y teniendo en cuenta que mis flip-flops son de la familia TTL(74ls73); ¿es factible la utilización de un decodificador de la familia CMOS(CD4511)?; me refiero especificamente a un modelo real, puesto que en la simulacion no supone ningun problem. Segun algunas personas de mi entorno el uso de ambas familias en un mismo circuito y en trabajos de baja frecuencia no afecta el funcionamiento general.