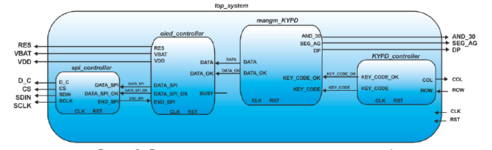

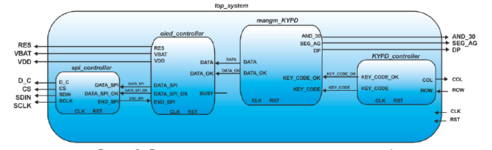

Hola a todos. estoy realizando un diseño basado en una placa Basys 3, con Vivado. El diseño se basa en 4 bloques interconectados.

En primer lugar, he realizado el diseño de spi_controller, cuya misión es establecer la comunicación con el Display oled.

Este bloque convertirá un dato paralelo que se le introduce por el puerto DATA_SPI de 9 bits (1 bit que indica si es un dato o un comando + 8 bits de dato/comando) y validado mediante la señal DATA_SPI_OK en un dato serie de 8 bits y un bit D_C. A su vez generará la señal SCLK del bus SPI y la señal de Chip Select (CS) del SPI.

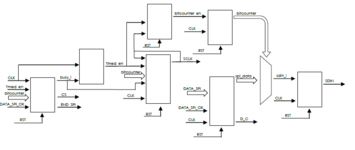

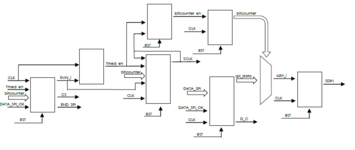

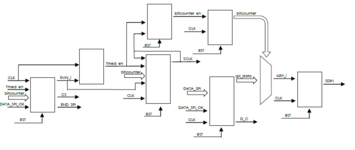

El esquema interno del spi_controller es el siguiente

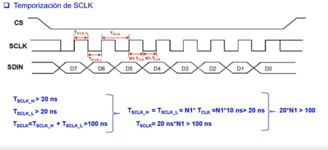

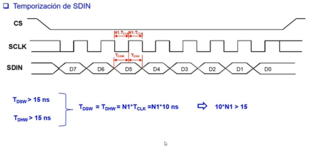

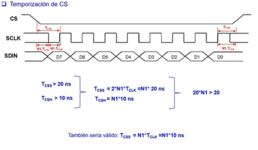

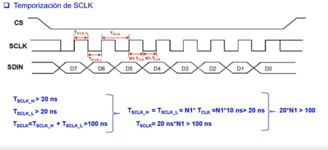

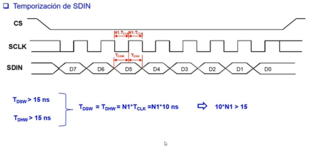

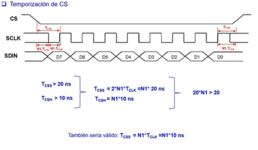

Y el código que he realizado es el que a continuación adjunto, teniendo en cuenta, unas restricciones temporales que pongo a continuación:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity spi_controller is

port ( CLK : in std_logic;

RST : in std_logic;

DATA_SPI_OK : in std_logic;

DATA_SPI : in std_logic_vector (8 downto 0);

D_C : out std_logic;

CS : out std_logic;

SDIN : out std_logic;

SCLK : out std_logic;

END_SPI : out std_logic);

end spi_controller;

architecture rtl of spi_controller is

-- señales para el prescaler

constant CLKmedDIV : integer := 5;

constant CLKsclkDIV : integer := 2;

signal Tmed_en : std_logic;

signal prescaler_cnt : integer range 0 to CLKmedDIV;

signal pres_sclk_cnt : integer range 0 to CLKsclkDIV;

-- señales para la señal busy

signal busy_i : std_logic;

signal busy_cnt : integer range 0 to 8;

-- señales para la SCLK

signal sclk_i : std_logic;

-- señales para el conteo de bits

signal bitcounter_en : std_logic;

signal bitcounter_cnt : integer range 8 downto 0;

signal bitcounter : std_logic_vector(3 downto 0);

-- selakes para el paralelo-serie

signal spi_data_i : std_logic_vector(7 downto 0);

signal sdin_i : std_logic;

begin

SCLK <= sclk_i;

CS <= not busy_i;

bitcounter <= std_logic_vector(to_unsigned(bitcounter_cnt,4));

-- prescaler para la temporización de Tmed (50ns)

process(CLK, RST)

begin

if (RST = '1') then

prescaler_cnt <= 0;

Tmed_en <= '0';

elsif (CLK'event and CLK = '1') then

Tmed_en <= '0';

if (busy_i = '1') then

if (prescaler_cnt = CLKmedDIV-1) then

prescaler_cnt <= 0;

Tmed_en <= '1';

else

prescaler_cnt <= prescaler_cnt+1;

end if;

end if;

end if;

end process;

-- prescaler para la temporización de SCLK (100ns)

process(CLK, RST)

begin

if (RST = '1') then

pres_sclk_cnt <= 0;

sclk_i <= '1';

elsif (CLK'event and CLK = '1') then

if (Tmed_en = '1' and busy_i = '1' and (bitcounter /= "0000" or sclk_i = '0')) then

sclk_i <= not sclk_i;

end if;

end if;

end process;

-- Generación de la señal Busy

process(CLK, RST)

begin

if (RST = '1') then

busy_i <= '0';

END_SPI <= '0';

elsif (CLK'event and CLK = '1') then

END_SPI <= '0';

-- busy_i <= not busy_i;

if (DATA_SPI_OK = '1') then

busy_i <= '1';

elsif (sclk_i = '1' and bitcounter = "0000" and Tmed_en = '1') then

busy_i <= '0';

if(busy_i <= '1') then

END_SPI <= '1';

end if;

end if;

end if;

end process;

-- Generador de señal para contar

process(Tmed_en, sclk_i)

begin

bitcounter_en <= '0';

if (Tmed_en = '1' and sclk_i = '1') then

bitcounter_en <= '1';

end if;

end process;

-- Contador de bits

process(CLK, RST)

begin

if (RST = '1') then

bitcounter_cnt <= 8;

elsif (CLK'event and CLK = '1') then

if (busy_i <= '1') then

if (bitcounter_en = '1') then

bitcounter_cnt <= bitcounter_cnt - 1;

if (bitcounter_cnt = 0) then

bitcounter_cnt <= 8;

end if;

end if;

end if;

end if;

end process;

-- Paralelo a serie

process(CLK, RST)

begin

if RST = '1' then

D_C <= '0';

elsif (CLK'event and CLK = '1') then

if (DATA_SPI_OK = '1') then

D_C <= DATA_SPI(8);

spi_data_i <= DATA_SPI(7 downto 0);

end if;

end if;

end process;

process(CLK, RST)

begin

if (RST = '1') then

SDIN <= '0';

elsif (CLK'event and CLK = '1') then

SDIN <= sdin_i;

end if;

end process;

process(spi_data_i, bitcounter)

begin

case bitcounter is

when "0111" =>

sdin_i <= spi_data_i(7);

when "0110" =>

sdin_i <= spi_data_i(6);

when "0101" =>

sdin_i <= spi_data_i(5);

when "0100" =>

sdin_i <= spi_data_i(4);

when "0011" =>

sdin_i <= spi_data_i(3);

when "0010" =>

sdin_i <= spi_data_i(2);

when "0001" =>

sdin_i <= spi_data_i(1);

when "0000" =>

sdin_i <= spi_data_i(0);

when others =>

sdin_i <= '0';

end case;

end process;

end rtl;

Ahora bien, he de realizar una modificación, el parámetro N1 que es el encargado de controlar los tiempos de la transmisión de un dato utilizando el protocolo SPI, se tiene que seleccionar con una constante de nombre cte_N1 y cuyo valor será 8.

ES aquí dónde me pierdo y no se como reflejarlo.

Podríais ayudarme?

Gracias

En primer lugar, he realizado el diseño de spi_controller, cuya misión es establecer la comunicación con el Display oled.

Este bloque convertirá un dato paralelo que se le introduce por el puerto DATA_SPI de 9 bits (1 bit que indica si es un dato o un comando + 8 bits de dato/comando) y validado mediante la señal DATA_SPI_OK en un dato serie de 8 bits y un bit D_C. A su vez generará la señal SCLK del bus SPI y la señal de Chip Select (CS) del SPI.

El esquema interno del spi_controller es el siguiente

Y el código que he realizado es el que a continuación adjunto, teniendo en cuenta, unas restricciones temporales que pongo a continuación:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity spi_controller is

port ( CLK : in std_logic;

RST : in std_logic;

DATA_SPI_OK : in std_logic;

DATA_SPI : in std_logic_vector (8 downto 0);

D_C : out std_logic;

CS : out std_logic;

SDIN : out std_logic;

SCLK : out std_logic;

END_SPI : out std_logic);

end spi_controller;

architecture rtl of spi_controller is

-- señales para el prescaler

constant CLKmedDIV : integer := 5;

constant CLKsclkDIV : integer := 2;

signal Tmed_en : std_logic;

signal prescaler_cnt : integer range 0 to CLKmedDIV;

signal pres_sclk_cnt : integer range 0 to CLKsclkDIV;

-- señales para la señal busy

signal busy_i : std_logic;

signal busy_cnt : integer range 0 to 8;

-- señales para la SCLK

signal sclk_i : std_logic;

-- señales para el conteo de bits

signal bitcounter_en : std_logic;

signal bitcounter_cnt : integer range 8 downto 0;

signal bitcounter : std_logic_vector(3 downto 0);

-- selakes para el paralelo-serie

signal spi_data_i : std_logic_vector(7 downto 0);

signal sdin_i : std_logic;

begin

SCLK <= sclk_i;

CS <= not busy_i;

bitcounter <= std_logic_vector(to_unsigned(bitcounter_cnt,4));

-- prescaler para la temporización de Tmed (50ns)

process(CLK, RST)

begin

if (RST = '1') then

prescaler_cnt <= 0;

Tmed_en <= '0';

elsif (CLK'event and CLK = '1') then

Tmed_en <= '0';

if (busy_i = '1') then

if (prescaler_cnt = CLKmedDIV-1) then

prescaler_cnt <= 0;

Tmed_en <= '1';

else

prescaler_cnt <= prescaler_cnt+1;

end if;

end if;

end if;

end process;

-- prescaler para la temporización de SCLK (100ns)

process(CLK, RST)

begin

if (RST = '1') then

pres_sclk_cnt <= 0;

sclk_i <= '1';

elsif (CLK'event and CLK = '1') then

if (Tmed_en = '1' and busy_i = '1' and (bitcounter /= "0000" or sclk_i = '0')) then

sclk_i <= not sclk_i;

end if;

end if;

end process;

-- Generación de la señal Busy

process(CLK, RST)

begin

if (RST = '1') then

busy_i <= '0';

END_SPI <= '0';

elsif (CLK'event and CLK = '1') then

END_SPI <= '0';

-- busy_i <= not busy_i;

if (DATA_SPI_OK = '1') then

busy_i <= '1';

elsif (sclk_i = '1' and bitcounter = "0000" and Tmed_en = '1') then

busy_i <= '0';

if(busy_i <= '1') then

END_SPI <= '1';

end if;

end if;

end if;

end process;

-- Generador de señal para contar

process(Tmed_en, sclk_i)

begin

bitcounter_en <= '0';

if (Tmed_en = '1' and sclk_i = '1') then

bitcounter_en <= '1';

end if;

end process;

-- Contador de bits

process(CLK, RST)

begin

if (RST = '1') then

bitcounter_cnt <= 8;

elsif (CLK'event and CLK = '1') then

if (busy_i <= '1') then

if (bitcounter_en = '1') then

bitcounter_cnt <= bitcounter_cnt - 1;

if (bitcounter_cnt = 0) then

bitcounter_cnt <= 8;

end if;

end if;

end if;

end if;

end process;

-- Paralelo a serie

process(CLK, RST)

begin

if RST = '1' then

D_C <= '0';

elsif (CLK'event and CLK = '1') then

if (DATA_SPI_OK = '1') then

D_C <= DATA_SPI(8);

spi_data_i <= DATA_SPI(7 downto 0);

end if;

end if;

end process;

process(CLK, RST)

begin

if (RST = '1') then

SDIN <= '0';

elsif (CLK'event and CLK = '1') then

SDIN <= sdin_i;

end if;

end process;

process(spi_data_i, bitcounter)

begin

case bitcounter is

when "0111" =>

sdin_i <= spi_data_i(7);

when "0110" =>

sdin_i <= spi_data_i(6);

when "0101" =>

sdin_i <= spi_data_i(5);

when "0100" =>

sdin_i <= spi_data_i(4);

when "0011" =>

sdin_i <= spi_data_i(3);

when "0010" =>

sdin_i <= spi_data_i(2);

when "0001" =>

sdin_i <= spi_data_i(1);

when "0000" =>

sdin_i <= spi_data_i(0);

when others =>

sdin_i <= '0';

end case;

end process;

end rtl;

Ahora bien, he de realizar una modificación, el parámetro N1 que es el encargado de controlar los tiempos de la transmisión de un dato utilizando el protocolo SPI, se tiene que seleccionar con una constante de nombre cte_N1 y cuyo valor será 8.

ES aquí dónde me pierdo y no se como reflejarlo.

Podríais ayudarme?

Gracias