Hola de nuevo foro,

Había publicado la siguiente idea propia que he probado y funciona muy bien en la esperanza que sea útil para alguien más, lo había hecho con un link a mi blog pero al parecer no está permitido. Pido disculpas públicamente por el mal entendido y coloco aquí la idea:

Hace algunos días encontré la solución a una necesidad, bastante específica tal vez, que llevaba un tiempo sin resolver: Necesitaba un bus de datos unidireccional de dos cables que, además de ser resistente a interferencias y fácil de implementar, los dispositivos esclavos pudiesen alimentarse desde él.

Como la planificación del proyecto para el que necesitaba el bus lo permitía, me permití dedicar durante algunas semanas unas cuantas horas a la búsqueda de una solución que supliese mi necesidad. Encontré al menos una docena de buses de dos cables y al menos la mitad de ellos proveen alimentación, pero ninguno me convenció, principalmente porque todos cubrían mucho más de lo que necesitaba lo cual los hacía ineficientes.

Finalmente al ver que la solución era crear un nuevo bus de dos cables, decidí bautizarlo con el nombre Yabotac del acrónimo en inglés "yet another bus of two alimentation cables" (otro bus de dos cables de alimentación), también lo llamo "2 wires" como un nombre más corto inspirado en "one wire", un popular bus cuya única semejanza con el mío es el nombre.

Al verlo funcionar me pareció buena idea publicar mi invento con la esperanza de que pueda resultar útil a alguien más.

El bus Yabotac (2 wires)

Aporta

* Comunicación resistente a ruido y alimentación estable en dos cables, los datos se transfieren de manera unidireccional y a alta velocidad entre un dispositivo de solo escritura, y n dispositivos de solo lectura.

Características

* Debe haber conectado al menos un dispositivo maestro y uno o más dispositivos esclavos.

* No requiere tiempos de espera, la sincronización de los datos se realiza mediante la señal de clock emitida por el maestro.

* A diferencia de otros buses de dos cables, se pueden transmitir la cantidad de 0 ó 1 contiguos que sean necesarios sin que caiga la tensión de la línea.

* La alimentación puede ser usada simultáneamente por otros dispositivos conectados, sin que estos interfieran en la transferencia de datos, como por ejemplo LEDs, altavoces, baterías e incluso servos, motores steppers y brushless (testeado).

* Muy resistente a interferencias, sus cables pueden compartir conductos con cables de tensión.

* Soporta implementaciones con cables tan largos como sea necesario.

* La velocidad de transferencia depende prácticamente de los dispositivos conectados y de las características físicas del cable.

* Los datos viajan en una sola dirección, partiendo desde el maestro y siendo recibidos por todos los esclavos. El descubrimiento y la selección de dispositivos conectados se realiza en la siguiente capa.

Diseño

El bus consta de dos líneas de comunicación identificadas: 1-Clock y 2-Data. Trabaja con tecnología TTL y cualquiera de sus dos líneas puede estar en estado "Alto" o "Bajo", pero en ningún caso en alta impedancia o, lo que es lo mismo, abiertas.

Funciona en dos estados: Reposo y Transferencia. Como su nombre lo sugiere durante el estado de reposo no se transmiten datos y la corriente en la línea es continua, por el contrario en el estado de transferencia la corriente es alterna y su frecuencia y valor eficaz dependen de la velocidad y longitud de los pulsos del reloj.

Al carecer de tiempos especificados por el bus, la velocidad de transferencia depende exclusivamente de la frecuencia de los pulsos de reloj manejado por el dispositivo maestro.

Cada bit de datos es enviado en un pulso de reloj.

Estado de reposo

El dispositivo maestro es el responsable de alimentar todos los dispositivos conectados al bus, con esta responsabilidad implícitamente tiene la obligación de encenderlos y para ello inicializa el bus en este estado. Así mismo el estado de reposo puede ser usado para que una capa superior indique o detecte el final del envío de datos.

Debido a que los datos viajan por el bus en un solo sentido el maestro no puede saber cuando los dispositivos conectados están listos para recibirlos, por ello al inicializar el bus este debe permanecer en estado de reposo como mínimo el tiempo que tarden en estar listos los dispositivos que el maestro tiene configurados como posiblemente conectados.

Para establecer el estado de reposo el maestro mantiene una de las líneas en "alto" y la otra en "bajo", sin importar cual sea. La corriente continua en los cables además de alimentar a los esclavos les indica que no hay datos para leer.

Transmisión

La transmisión de datos se realiza de a un bit por cada ciclo de reloj. Para transferir un bit el maestro tira la tensión manteniendo ambas líneas a masa durante medio ciclo, luego pone en "Alto" la línea de datos para escribir un 1 lógico en el bus o bien pone en "Alto" la línea de reloj para escribir un 0 en el bus, las líneas son mantenidas en este estado durante al menos medio ciclo.

Medio ciclo de reloj es, en una implementación optima, el tiempo que necesita la electrónica de los receptores para detectar el cambio de "Alto" a "Bajo" en cualquiera de sus líneas, de todas formas las simplicidad del diseño de este bus hace que no dependa de tiempos, permitiendo incluso variar la frecuencia de los pulsos, esta flexibilidad podría ser aprovechada en la siguiente capa para discriminar mensajes de datos y control por ejemplo.

Si habéis sido perspicaces os habréis dado cuenta que el bus queda naturalmente en estado de reposo tras la transmisión de cada bit, por lo que no es necesario hacer nada más para transicionar de estado.

Recepción

Cuando el dispositivo esclavo se enciende forzosamente debe ver la línea de reloj en "Alto", esto significa que hay corriente en el bus, cosa que es bastante lógica teniendo en cuenta que se alimenta desde él. No detectar en "Alto" la linea de clock al momento de arrancar debe ser identificado por el dispositivo esclavo como un fallo en la electrónica.

Para leer un bit, la rutina de recepción debe esperar que la línea de clock cambie a estado "Bajo" y luego a estado "Alto", cuando esto suceda debe leer directamente el valor de su línea de datos y esperar al siguiente pulso de reloj.

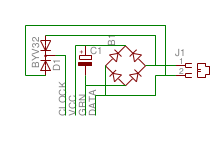

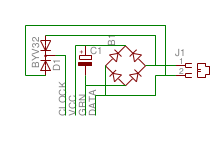

Esquemático del lado esclavo

Como se puede ver en el siguiente esquemático, la línea de Clock estará en alto en tanto circule corriente entre los conectores 1 y 2, sin importar el sentido en el que esta circule.

Por otro lado la línea de Data es solidaria a la del maestro, de tal forma que si el emisor la pone en "Alto" leeremos un 1 lógico y si está en "Bajo", con la línea de clock en "Alto", leeremos un 0 lógico.

A su vez ambas entran en el rectificador cuya salida ofrece una alimentación estable ya que en el caso más extremo de uso del bus a alta velocidad hay corriente en este 1/2 ciclo de cada ciclo, cosa que es compatible con los estándares de alimentación para los buses de este tipo.

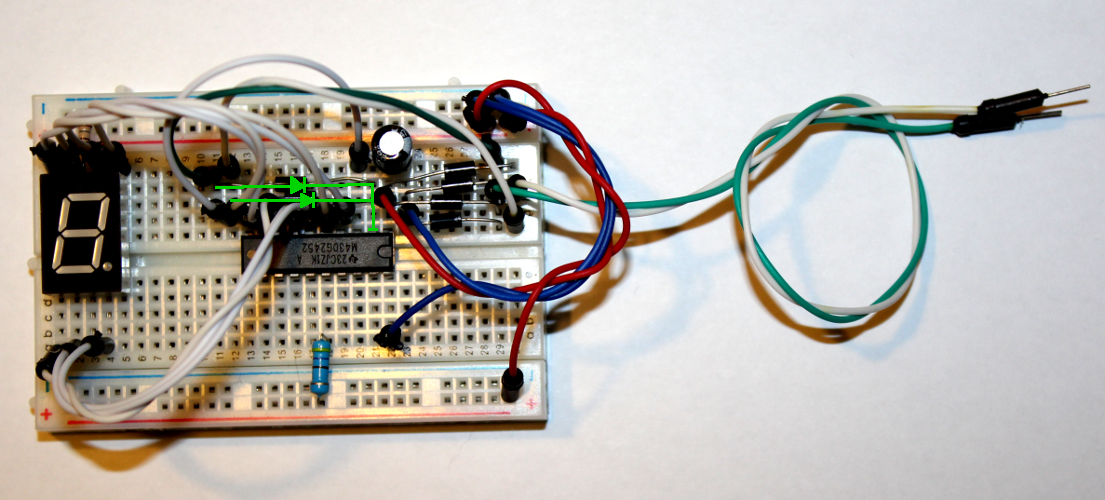

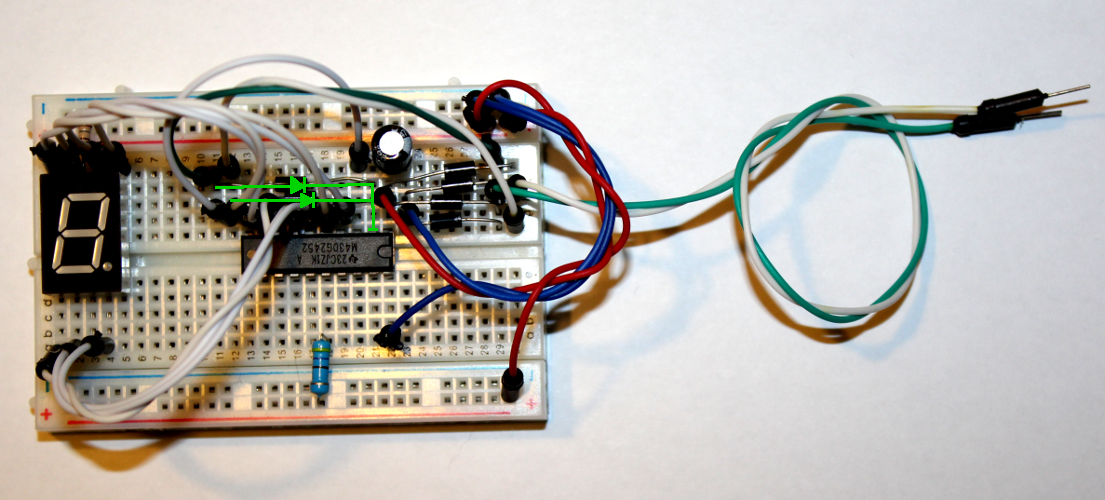

Algunos detalles de mi primera implementación

Este bus lo cree con la idea de usarlo para transmitir datos hacia un display, para pruebas de concepto monté el siguente breadboard el cual luego me vino muy bien como probador. Con él he descubierto algunos detalles interesantes a la hora de implementarlo.

He pintado en verde los diodos que conectan ambas líneas del bus a la pata 2 del MSP, la cual tengo asignada para el clock. Si seguís el camino del cable blanco conectado al diodo más corto, veréis que une directamente el cable blanco del bus con la tercera pata del MSP, la cual he asignado como data.

Algunos datos a tener en cuenta

* Si se inicializa el bus siempre de la misma forma, por ejemplo con un 1 lógico, en los esclavos se puede añadir lógica para que autodetecten como está conectado mirando el valor de Data al arrancar y ahorrar así el tener que identificar los cables y conexiones.

* Es aconsejable enrollar los cables del bus si se van a poner en bandejas o conductos junto a otros cables de corriente elevada. Debido a su tecnología TTL el bus detecta la tensión en una línea en función de su voltaje de referencia en la otra, por lo tanto si ambos cables viajan juntos y se induce una corriente desde cables paralelos, esta entrará en ambos cables elevando también el voltaje de referencia, de esta forma se anulará el ruido en tanto los componentes de la implementación lo soporten.

* No he encontrado nada similar a esta idea hasta el día de hoy, por lo tanto la publico aquí nombrándome autor de la misma y, como una excepción al resto de entradas de mi blog, bajo licencia CC by-sa 3.0, lo que significa en pocas palabras que puedes copiar, distribuir y adaptar este trabajo con o sin fines lucrativos siempre que se me nombre y reconozca como autor del mismo o de la base de sus trabajos derivados (lo que no significa puedes decir que yo recomiendo trabajos derivados de este sin mi autorización), y que los trabajos derivados de este se publiquen bajo una licencia similar. Puedes encontrar aquí una copia del documento legal de la licencia: http://creativecommons.org/licenses/by-sa/3.0/legalcode

En cuanto el tiempo me lo permita publicaré en otra entrada el código fuente que yo uso en siguiente capa de comunicación del bus.

Había publicado la siguiente idea propia que he probado y funciona muy bien en la esperanza que sea útil para alguien más, lo había hecho con un link a mi blog pero al parecer no está permitido. Pido disculpas públicamente por el mal entendido y coloco aquí la idea:

Hace algunos días encontré la solución a una necesidad, bastante específica tal vez, que llevaba un tiempo sin resolver: Necesitaba un bus de datos unidireccional de dos cables que, además de ser resistente a interferencias y fácil de implementar, los dispositivos esclavos pudiesen alimentarse desde él.

Como la planificación del proyecto para el que necesitaba el bus lo permitía, me permití dedicar durante algunas semanas unas cuantas horas a la búsqueda de una solución que supliese mi necesidad. Encontré al menos una docena de buses de dos cables y al menos la mitad de ellos proveen alimentación, pero ninguno me convenció, principalmente porque todos cubrían mucho más de lo que necesitaba lo cual los hacía ineficientes.

Finalmente al ver que la solución era crear un nuevo bus de dos cables, decidí bautizarlo con el nombre Yabotac del acrónimo en inglés "yet another bus of two alimentation cables" (otro bus de dos cables de alimentación), también lo llamo "2 wires" como un nombre más corto inspirado en "one wire", un popular bus cuya única semejanza con el mío es el nombre.

Al verlo funcionar me pareció buena idea publicar mi invento con la esperanza de que pueda resultar útil a alguien más.

El bus Yabotac (2 wires)

Aporta

* Comunicación resistente a ruido y alimentación estable en dos cables, los datos se transfieren de manera unidireccional y a alta velocidad entre un dispositivo de solo escritura, y n dispositivos de solo lectura.

Características

* Debe haber conectado al menos un dispositivo maestro y uno o más dispositivos esclavos.

* No requiere tiempos de espera, la sincronización de los datos se realiza mediante la señal de clock emitida por el maestro.

* A diferencia de otros buses de dos cables, se pueden transmitir la cantidad de 0 ó 1 contiguos que sean necesarios sin que caiga la tensión de la línea.

* La alimentación puede ser usada simultáneamente por otros dispositivos conectados, sin que estos interfieran en la transferencia de datos, como por ejemplo LEDs, altavoces, baterías e incluso servos, motores steppers y brushless (testeado).

* Muy resistente a interferencias, sus cables pueden compartir conductos con cables de tensión.

* Soporta implementaciones con cables tan largos como sea necesario.

* La velocidad de transferencia depende prácticamente de los dispositivos conectados y de las características físicas del cable.

* Los datos viajan en una sola dirección, partiendo desde el maestro y siendo recibidos por todos los esclavos. El descubrimiento y la selección de dispositivos conectados se realiza en la siguiente capa.

Diseño

El bus consta de dos líneas de comunicación identificadas: 1-Clock y 2-Data. Trabaja con tecnología TTL y cualquiera de sus dos líneas puede estar en estado "Alto" o "Bajo", pero en ningún caso en alta impedancia o, lo que es lo mismo, abiertas.

Funciona en dos estados: Reposo y Transferencia. Como su nombre lo sugiere durante el estado de reposo no se transmiten datos y la corriente en la línea es continua, por el contrario en el estado de transferencia la corriente es alterna y su frecuencia y valor eficaz dependen de la velocidad y longitud de los pulsos del reloj.

Al carecer de tiempos especificados por el bus, la velocidad de transferencia depende exclusivamente de la frecuencia de los pulsos de reloj manejado por el dispositivo maestro.

Cada bit de datos es enviado en un pulso de reloj.

Estado de reposo

El dispositivo maestro es el responsable de alimentar todos los dispositivos conectados al bus, con esta responsabilidad implícitamente tiene la obligación de encenderlos y para ello inicializa el bus en este estado. Así mismo el estado de reposo puede ser usado para que una capa superior indique o detecte el final del envío de datos.

Debido a que los datos viajan por el bus en un solo sentido el maestro no puede saber cuando los dispositivos conectados están listos para recibirlos, por ello al inicializar el bus este debe permanecer en estado de reposo como mínimo el tiempo que tarden en estar listos los dispositivos que el maestro tiene configurados como posiblemente conectados.

Para establecer el estado de reposo el maestro mantiene una de las líneas en "alto" y la otra en "bajo", sin importar cual sea. La corriente continua en los cables además de alimentar a los esclavos les indica que no hay datos para leer.

Transmisión

La transmisión de datos se realiza de a un bit por cada ciclo de reloj. Para transferir un bit el maestro tira la tensión manteniendo ambas líneas a masa durante medio ciclo, luego pone en "Alto" la línea de datos para escribir un 1 lógico en el bus o bien pone en "Alto" la línea de reloj para escribir un 0 en el bus, las líneas son mantenidas en este estado durante al menos medio ciclo.

Medio ciclo de reloj es, en una implementación optima, el tiempo que necesita la electrónica de los receptores para detectar el cambio de "Alto" a "Bajo" en cualquiera de sus líneas, de todas formas las simplicidad del diseño de este bus hace que no dependa de tiempos, permitiendo incluso variar la frecuencia de los pulsos, esta flexibilidad podría ser aprovechada en la siguiente capa para discriminar mensajes de datos y control por ejemplo.

Si habéis sido perspicaces os habréis dado cuenta que el bus queda naturalmente en estado de reposo tras la transmisión de cada bit, por lo que no es necesario hacer nada más para transicionar de estado.

Recepción

Cuando el dispositivo esclavo se enciende forzosamente debe ver la línea de reloj en "Alto", esto significa que hay corriente en el bus, cosa que es bastante lógica teniendo en cuenta que se alimenta desde él. No detectar en "Alto" la linea de clock al momento de arrancar debe ser identificado por el dispositivo esclavo como un fallo en la electrónica.

Para leer un bit, la rutina de recepción debe esperar que la línea de clock cambie a estado "Bajo" y luego a estado "Alto", cuando esto suceda debe leer directamente el valor de su línea de datos y esperar al siguiente pulso de reloj.

Esquemático del lado esclavo

Como se puede ver en el siguiente esquemático, la línea de Clock estará en alto en tanto circule corriente entre los conectores 1 y 2, sin importar el sentido en el que esta circule.

Por otro lado la línea de Data es solidaria a la del maestro, de tal forma que si el emisor la pone en "Alto" leeremos un 1 lógico y si está en "Bajo", con la línea de clock en "Alto", leeremos un 0 lógico.

A su vez ambas entran en el rectificador cuya salida ofrece una alimentación estable ya que en el caso más extremo de uso del bus a alta velocidad hay corriente en este 1/2 ciclo de cada ciclo, cosa que es compatible con los estándares de alimentación para los buses de este tipo.

Algunos detalles de mi primera implementación

Este bus lo cree con la idea de usarlo para transmitir datos hacia un display, para pruebas de concepto monté el siguente breadboard el cual luego me vino muy bien como probador. Con él he descubierto algunos detalles interesantes a la hora de implementarlo.

He pintado en verde los diodos que conectan ambas líneas del bus a la pata 2 del MSP, la cual tengo asignada para el clock. Si seguís el camino del cable blanco conectado al diodo más corto, veréis que une directamente el cable blanco del bus con la tercera pata del MSP, la cual he asignado como data.

Algunos datos a tener en cuenta

* Si se inicializa el bus siempre de la misma forma, por ejemplo con un 1 lógico, en los esclavos se puede añadir lógica para que autodetecten como está conectado mirando el valor de Data al arrancar y ahorrar así el tener que identificar los cables y conexiones.

* Es aconsejable enrollar los cables del bus si se van a poner en bandejas o conductos junto a otros cables de corriente elevada. Debido a su tecnología TTL el bus detecta la tensión en una línea en función de su voltaje de referencia en la otra, por lo tanto si ambos cables viajan juntos y se induce una corriente desde cables paralelos, esta entrará en ambos cables elevando también el voltaje de referencia, de esta forma se anulará el ruido en tanto los componentes de la implementación lo soporten.

* No he encontrado nada similar a esta idea hasta el día de hoy, por lo tanto la publico aquí nombrándome autor de la misma y, como una excepción al resto de entradas de mi blog, bajo licencia CC by-sa 3.0, lo que significa en pocas palabras que puedes copiar, distribuir y adaptar este trabajo con o sin fines lucrativos siempre que se me nombre y reconozca como autor del mismo o de la base de sus trabajos derivados (lo que no significa puedes decir que yo recomiendo trabajos derivados de este sin mi autorización), y que los trabajos derivados de este se publiquen bajo una licencia similar. Puedes encontrar aquí una copia del documento legal de la licencia: http://creativecommons.org/licenses/by-sa/3.0/legalcode

En cuanto el tiempo me lo permita publicaré en otra entrada el código fuente que yo uso en siguiente capa de comunicación del bus.