Esta vez les consulto para que me ayuden a interpretar los graficos de unos datasheets.

La memoria es: IS61C256AH (en realidad es T14M256A-12ns pero en la de issi estan mas claros los datos y son compatibles)

El ADC es: ADS831

Adjunto las capturas de pantalla de sus respectivos datasheets.

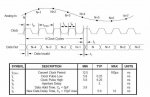

Empiezo por la memoria:

Para grabar en ella, estoy llevando ~OE a nivel alto, durante toda la captura (los 32K) a fin de poner las entrada/salida en alta impedancia y no tener la demora de controlar con OE la grabacion.

Mi consulta es: Segun interpreto yo, hay que setear la direccion primero y los datos se grabaran un poco despues del flanco descendente de ~WE

¿Es correcta esta interpretacion? Voy a trabajar cerca de los 80mhz asi que el tiempo es critico.

Los contadores que uso para direccionar la memoria son dos 4040 en cascada. Cambian la direccion en flanco descendente de reloj.

Por otro lado, el ADC:

Segun interpreto, el mismo pone los datos de una conversion en sus salidas luego del flanco descendente del reloj. (y samplea en flanco ascendente). ¿Es correcto esto?

Si tengo en cuenta el pipeline de 4 ciclos de reloj, pero es anecdotico para mi duda creo.

En resumen, creo que el orden es:

Con OE de la memoria en estado ALTO permanente:

1)- Setear direccion, bajando el clock de los contadores

2)- Luego, bajar el clock del ADC para que ponga los datos en la salida

3)- Luego, bajar WR en la memoria

4)- Asegurarse que el clock de contadores no vuelva a hacer el ciclo (ascender, descender) hasta que WE no se haya elevado.

Estos tiempos y retrasos los estoy haciendo en el circuito de relojeria implementado con compuertas NAND y NOT schmitt trigger

La memoria es: IS61C256AH (en realidad es T14M256A-12ns pero en la de issi estan mas claros los datos y son compatibles)

El ADC es: ADS831

Adjunto las capturas de pantalla de sus respectivos datasheets.

Empiezo por la memoria:

Para grabar en ella, estoy llevando ~OE a nivel alto, durante toda la captura (los 32K) a fin de poner las entrada/salida en alta impedancia y no tener la demora de controlar con OE la grabacion.

Mi consulta es: Segun interpreto yo, hay que setear la direccion primero y los datos se grabaran un poco despues del flanco descendente de ~WE

¿Es correcta esta interpretacion? Voy a trabajar cerca de los 80mhz asi que el tiempo es critico.

Los contadores que uso para direccionar la memoria son dos 4040 en cascada. Cambian la direccion en flanco descendente de reloj.

Por otro lado, el ADC:

Segun interpreto, el mismo pone los datos de una conversion en sus salidas luego del flanco descendente del reloj. (y samplea en flanco ascendente). ¿Es correcto esto?

Si tengo en cuenta el pipeline de 4 ciclos de reloj, pero es anecdotico para mi duda creo.

En resumen, creo que el orden es:

Con OE de la memoria en estado ALTO permanente:

1)- Setear direccion, bajando el clock de los contadores

2)- Luego, bajar el clock del ADC para que ponga los datos en la salida

3)- Luego, bajar WR en la memoria

4)- Asegurarse que el clock de contadores no vuelva a hacer el ciclo (ascender, descender) hasta que WE no se haya elevado.

Estos tiempos y retrasos los estoy haciendo en el circuito de relojeria implementado con compuertas NAND y NOT schmitt trigger