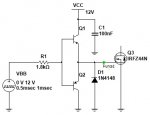

A ok. El transistor mosfet trabaja como interruptor con una carga resistiva de 3 ohms, el arreglo push pull (transistores NPN y PNP), me debe entregar una corriente de 500mA, y una tensión mayor de 10V (para la compuerta del transistor). Cuando VBB = 12V, el NPN conduce y el PNP está en corto, y si VBB = 0V, el NPN está en corte y la corriente se descarga por el PNP. El transistor NPN debe trabajar en la región lineal para poder reducir el tiempo de recarga (tr) para las capacitancias parásitas del MOSFET. La señal es de VGS.

La corriente IG debe ser de 461mA, por es elegí IC = 500mA. La hFE a esa corriente es 80 y el VBE es 0,8V.

La gráfica es simulada, ya que no cuento con osciloscopio, pero necesito documentarlo (mi profesor dijo que no habría problema). El circuito funciona ya que el MOSFET no se calienta. Pero quería ver si se puede eliminar en la simulación, porque se que me van a preguntar.

/**********************************************************************************/

Bueno, gracias chclau, sabiendo que es un offset y no un desfase, pude encontrar la solución en el foro, colocando una resistencia del gate a un voltaje negativo se elimina y como el más cercano que tengo es GND, lo simule y funciono. Aquí la señal: