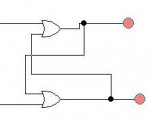

Es posible crear o obtener un tipo de Flip flop con compuertas OR??

he visto con compuertas NAND, con compuertas NOR y NOT, pero no he podido encontrar el fundamento teórico para hacer un FLIP FLOP solo con compuertas OR, sin inversores.

o en su defecto porque solo se puede con compuertas negadas?

espero me aporte sus conocimiento o recomienden una lectura especifica a estos temas ya busque en google y algunos libros de lectronica digital, pero no identifico de forma puntual lo que aquí pregunto.

gracias

he visto con compuertas NAND, con compuertas NOR y NOT, pero no he podido encontrar el fundamento teórico para hacer un FLIP FLOP solo con compuertas OR, sin inversores.

o en su defecto porque solo se puede con compuertas negadas?

espero me aporte sus conocimiento o recomienden una lectura especifica a estos temas ya busque en google y algunos libros de lectronica digital, pero no identifico de forma puntual lo que aquí pregunto.

gracias

Adjuntos

Última edición: