Hola a todos electronicos y protonicos.

Necesito hacer un circuito de tipo sample and hold para una conversion analogo-digital, la idea es en realidad un conversor de tiempo a digital, para ello se usa un integrador como un conversor de tiempo a amplitud y luego un A/D. Posteo aqui por que mi duda radica en la parte analogica del asunto.

Una explicación de lo anterior (Stephan Henzler Time-to-Digital Converters):

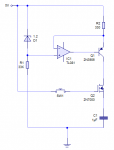

Este es mi circuito:

El problema es que el capacitor (es de 470pF de mica) no retiene el voltaje por mucho tiempo, segun lo que puede observar en el osciloscopio le toma unos 8 ms descargarse en la clasica forma exponencial.

Mi pregunta es, como debo hacer para asegurar una lectura correcta en el ADC? esta deberia ser el voltaje pico que alcanza el capacitor y no el voltaje en plena descarga o ya descargado por completo...

Gracias.

Necesito hacer un circuito de tipo sample and hold para una conversion analogo-digital, la idea es en realidad un conversor de tiempo a digital, para ello se usa un integrador como un conversor de tiempo a amplitud y luego un A/D. Posteo aqui por que mi duda radica en la parte analogica del asunto.

Una explicación de lo anterior (Stephan Henzler Time-to-Digital Converters):

Este es mi circuito:

El problema es que el capacitor (es de 470pF de mica) no retiene el voltaje por mucho tiempo, segun lo que puede observar en el osciloscopio le toma unos 8 ms descargarse en la clasica forma exponencial.

Mi pregunta es, como debo hacer para asegurar una lectura correcta en el ADC? esta deberia ser el voltaje pico que alcanza el capacitor y no el voltaje en plena descarga o ya descargado por completo...

Gracias.