Hola crazysound, el nucleo es un T157-2 que compre por ebay.Hola quercus10, creo que ese pcb va por muy buen camino. Cuál es el nombre de ese núcleo?

Saludos..

Saludos..

Follow along with the video below to see how to install our site as a web app on your home screen.

Nota: This feature currently requires accessing the site using the built-in Safari browser.

Hola crazysound, el nucleo es un T157-2 que compre por ebay.Hola quercus10, creo que ese pcb va por muy buen camino. Cuál es el nombre de ese núcleo?

Saludos..

Saludos..

Hola Amigos estoy reuniendo los componentes para armar este amplificador y ampliar mis conocimientos pero tengo el problema que en mi ciudad consigo unos condensadores grandes de 1uF y de poliéster y en el diagrama dice que deben de ser de 1uF cerámicos ………… me pregunto será que condensadores de 100nF me pueden servir o puedo colocar electrolíticos 1uF????

Otra cosa en la tabla que aparece en el aporte de ejtagle que dice las modificaciones que toca hacer según la alimentación no aparece la que tengo +/-70V aparecen para 57V o 80V .

En este caso puedo trabajar con los datos para 80V?

Adjunto el cambio que propone Ejtagle.

A ver que opina Ejtagle..Hay que ser cautelosos con el cambio propuesto, ya que si bien se baja la disipación de cada transistor del par diferencial, el ruido se empieza a ir por las nubes. Hay soluciones técnicas más adecuadas para el caso particular.

Saludos

Hay que ser cautelosos con el cambio propuesto, ya que si bien se baja la disipación de cada transistor del par diferencial, el ruido se empieza a ir por las nubes. Hay soluciones técnicas más adecuadas para el caso particular.

Saludos

Si fuera un par diferencial para amplificar audio, te daría toda la razón. Pero, en este caso, simplemente es un conversor de nivel de desbalanceado a balanceado.

A lo que me refería como una más adecuada solución técnica que esas dos resistencias de 10 K era justamente la opción que ud. mencionó de cascodear la salida de esos dos colectores del par diferencial. La misma solución es posible también para la salida de la fuente de corriente constante que alimenta al par diferencial.

En cuanto al ruido introducido por esas resistencias en esos puntos (por más que sea en el camino de una señal digital de alta frecuencia), personalmente evitaría por todos los medios introducir "batidos" adicionales al asunto. Recuerde que una simple resistencia en cada uno de esos puntos se puede convertir en una hermosa antena, si es recorrida por una señal de HF (no es lo mismo una resistencia física que la dinámica presentada por la salida de un transistor para una señal de HF!!!). Es más, sería más interesante que largas explicaciones técnicas y posturas, una visualización con osciloscopio del cambio que pueda suscitarse con o sin esas resistencias. ¿No cree?

Saludos

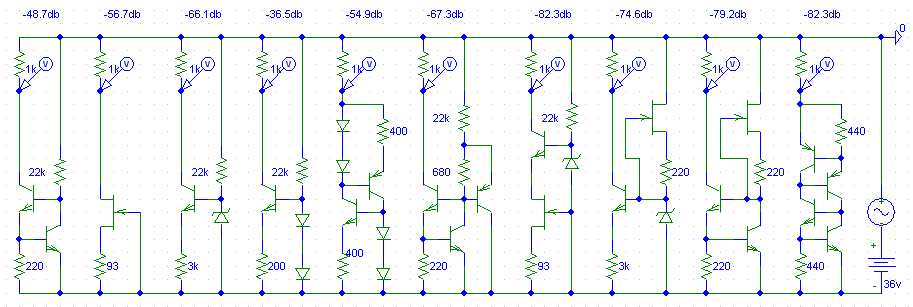

Resultan interesantes los cuatro escenarios que ha comparado y simulado.

Es llamativo que dé más lento con las resistencias de 10 K dispuestas entre cada colector del par diferencial y esas resistencias de 2K2, siendo que la corriente que proviene de cada colector no se vería modificada teóricamente con el agregado de esas mismas, si el voltaje de alimentación y los parámetros vinculados a la situación particular lo permiten. La capacidad parásita de cada entrada del IR "ve" 2K2 en un sentido y "ve" una fuente de corriente hacia un colector en otro sentido (para descarga/carga, respectivamente). Obviamente, a la fuente de corriente vista hacia cada colector hay que sumarle esos 10 K (que en condiciones ideales no influirían en los resultados finales, por ser ésta infinita). Ambos tiempos deberían resultar bien diferentes y, también, las formas de acumularse esos mismos tiempos (rampa lineal en un caso y exponencial en otro caso).

La sospecha que tengo es que la impedancia vista hacia cada colector (viéndolo desde cada entrada del IR hacia cada colector del par) no sea tan grande como uno la espera (calculo en torno a unos 11,36 K aprox., según mis gruesos tanteos, acorde a la relación de incremento de tiempos de 25 nS a 47 nS, que no es poco cambio). El problema es que si cada colector no se comporta ya como una verdadera fuente de corriente (en cuanto a los parámetros característicos), alguna incidencia negativa puede esperarse al agregar esas resistencias.

¿Sería posible contrastar los resultados de las simulaciones contra los de situaciones prácticas?. Yo no tengo armado el circuito, por lo cual me resultaría imposible medirlo.

Imagínese que hay muchas cosas que a un simulador se le escapa, por más que incorporemos la mayor cantidad de variables posibles.

Recuerde que es un diseño más cercano a los cuidados propios de RF que a los de BF.

Saludos

La fuente de corriente no es totalmente estable.. Se ve una una variación transitoria de 500nA en el momento de la conmutación...Es decir que la impedancia de salida de la fuente de corriente no es infinita ni de casualidad..

Fijate que el Ing. Tagle esta hablando de capacidades de 1pf pero a la frecuencia de operacion de este ampli (mas las armonicas) las pistas del PCB tienen inductancias del orden de los 10nHy por cm (o mas) y capacidades casi del mismo orden que las que estas teniendo en cuenta en los semiconductores.

En esas condiciones es seguro que vas a tener diferencias significativas con el simulador, pero el analisis es completamente valido, y lo podes acercar a la realidad si consideras estos valores que estan distribuidos en el PCB.

Es muy obvio que existen todos esos parámetros distribuidos por todo el circuito (y, muy posiblemente, algunos más que ni imaginemos). Lo verdaderamente complicado es integrar todos esos parámetros en la simulación para que denote una respuesta lo más similar a una situación real. Vamos... que en la práctica muy pocos lo hacemos (por la complicación y limitación técnica que eso nos representa, que muy pocos admitimos no saberlo y que muy pocos conocemos) y tampoco es muy necesario hacerlo en determinadas circunstancias (por tiempo invertido => dinero; practicidad, etc.). El camino más fácil y concreto es la medición real de la situación.

Y no le resto validez a la simulación planteada (la veo perfecta), solo que sostengo y, el Ing. lo reconoce también, que hay cosas que superan a una necesidad práctica de la implementación en cuestión. Al fin de cuentas, ¿quién se va a complicar con todas esas especulaciones técnicas de lo que podría estar sucediendo internamente en las junturas de un transistor (de la que seguro nunca vamos a estar completamente convencidos si realmente sucede así), si con una simple medición lo puedo estar validando o refutando?