Buenas, a ver si alguien me puede ayudar porque por gogle no he encontrado nada al respecto.

El caso es que estoy creando la parte de alimentación de una placa y claro, quiero tener las menores pérdidas posibles y que no tenga inductancia alguna.

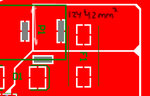

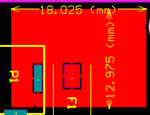

Para esto aconsejan planos como se puede ver en la imagen adjunta (Leído de fabricantes como Linear, Texas,etc).

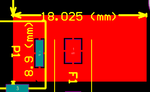

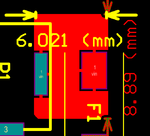

El problema que tengo es el espacio y quisiera saber cuánta área mínima puedo ocupar de la placa para tener una pérdida muy pequeña y de inductancia casi nada.

Es decir, necesito alguna ecuacion que me diga cuanta impedancia tiene un área de cobre de una placa de 1 oz.

Si alguien me pudiese ayudar con esta duda se lo agradecería.

El caso es que estoy creando la parte de alimentación de una placa y claro, quiero tener las menores pérdidas posibles y que no tenga inductancia alguna.

Para esto aconsejan planos como se puede ver en la imagen adjunta (Leído de fabricantes como Linear, Texas,etc).

El problema que tengo es el espacio y quisiera saber cuánta área mínima puedo ocupar de la placa para tener una pérdida muy pequeña y de inductancia casi nada.

Es decir, necesito alguna ecuacion que me diga cuanta impedancia tiene un área de cobre de una placa de 1 oz.

Si alguien me pudiese ayudar con esta duda se lo agradecería.