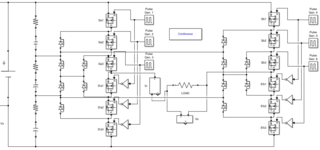

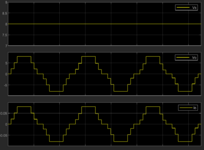

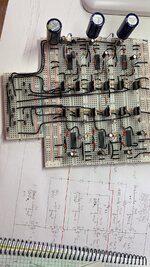

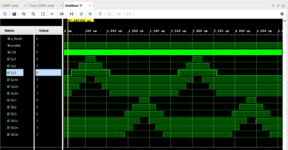

Hola, me llamo kikecea y estoy acabando mi ingeniería de electronica industrial y automática con el trabajo fin de grado. Estoy tratando de hacer un inversor multinivel con el diseño que os enseño en la fotografía. Tras muchas pruebas y diferentes diseños al final he conseguido que se me activen los transistores mosfet, lo único es que la señal que me aparece en el osciloscopio me pone de 1.2KHz y yo lo he diseñado para que sea de 400Hz. En el código Vhdl para la fpga utilizo esa base de tiempo y como veis en la simulación se respeta esa medida, incluso cuando mido las señales directamente en la salida de la placa de desarrollo Arty A7 las señales que me lee el osciloscopio son de 400Hz. Empiezo a dudar si será algo de como recibe la señal el osciloscopio o algo así... os enseño unas imágenes a ver si alguien me puede echar una mano... muchas gracias por vuestra ayuda