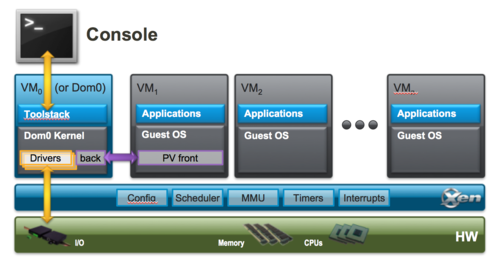

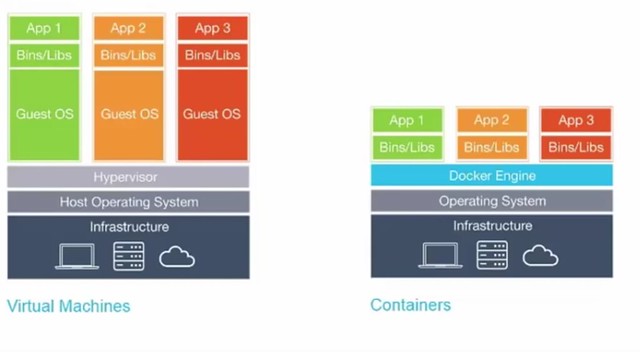

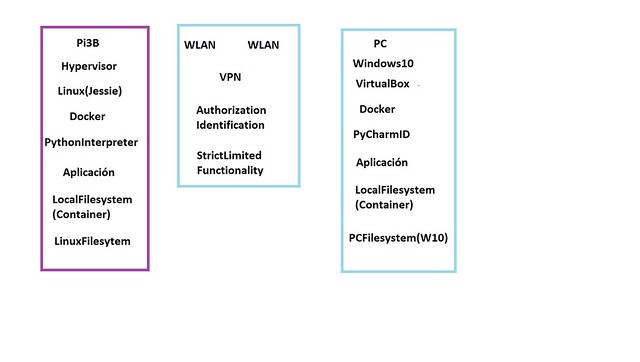

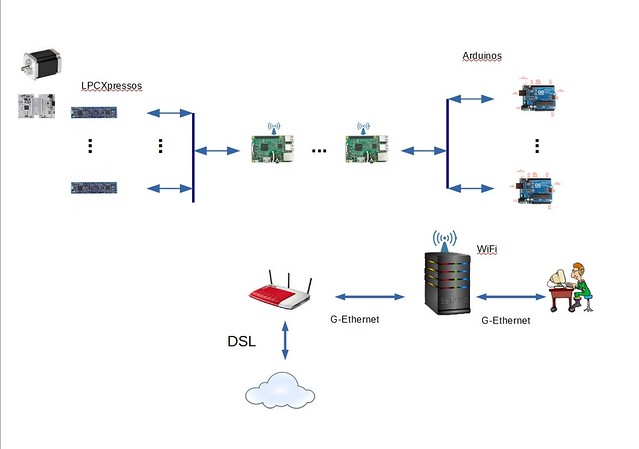

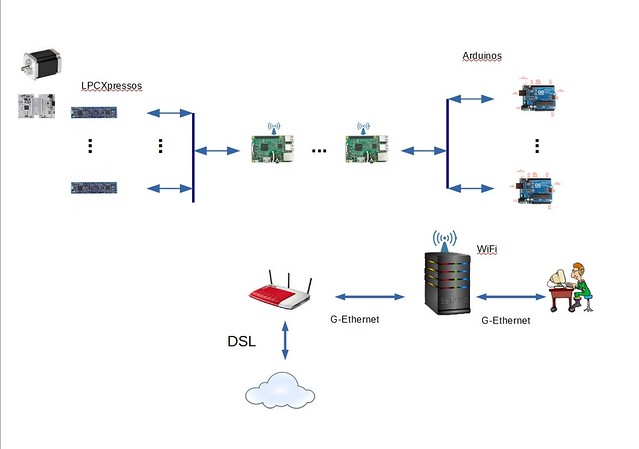

Hola amigos, resulta que como consecuencia de haber redefinido mi infraestructura informática de mi taller he descubierto para mi el tema de hypervisors y trustzone con foco a su adaptación en sistemas embebidos. me voy a meter de forma "real y física" con el tema de hipervisores del tipo 1, también llamados "bare metall" en el servidor. Publico aquí la imagen de la estructura muy burda, es la primera edición:

Tanto en mi PC, donde actualmente uso un i7 620, como con el Xenion X5550 a 2,67 GHz, uso procesadores con funcionalidad para operar hipervisor del tipo 1. Me compré 2 Xenion X5550 por solo 26,70 Euros incluyendo el costo del flete con LGA1366.

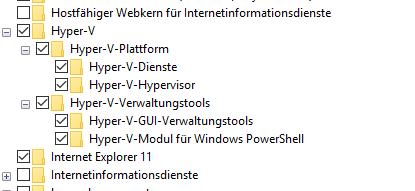

El hombrecito a la derecha abajo, yo y mi ordenador principalmente usa Windows 10, pero tengo un segundo disco duro con Ubuntu 16.04 TLS! Esto lo dejaré por ahora al menos, tal cual está. Ya estoy armándome el servidor con una placa madre ASUS P&t WS Professional a la cual le pondré unos de los procesadores Xenion 5550. Alí me voy a dedicar al reto de instalar el hipervisor tipo 1. Aún estoy investigando de que proveedor. Sobre el hipervisor pondré un entorno virtual con Windows 10 Pro y otra entorno virtual con Ubuntu 16.04 TLS.

Alguno de Ustedes ya tiene experiencias con hipervisores?

Por WiFi en el centro del gráfico ven las placas Raspi conectadas de forma inalámbrica con el servidor.

Aquí el enlace a un artículo muy interesante para mis objetivos y es que en controladores del tipo ARM Cortex basadas en la versión V8 la empresa ARM ha portado lo que llama Trustzone. Es funcionalidad de apoyo para la funcionalidad de hipervisor.

Voy a empezar a investigar cual proveedor ya es activo en este sector. las chances son muy buenas investigar en el entorno de los productos provenientes de Freescale en NXP. Esta es la parte del uso de la virtualización y el encapsulamiento lograble aislando partes de los programas en entornos virtuales proporcionados por estas funcionalidades.

Aquí un segundo artículo que consta de la "parte uno" y "la parte dos".

Esta serie de artículos a la que quiero sumar tales de la empresa "Mentor Graphics" se discute el tema de hipervisores como método de protección en sistemas embebidos con ejemplo a los entornos de sistemas embebidos en carros en general y de ciculación autónoma. Allí también cuentan que por ejemplo la industria de aviación ve en esta metodología una forma mas avanzada de proteger sus sistemas. Pero también las informaciones de la funcionalidad de hipervisores en sistemas embebidos, deep embedded, donde los tiempos de reacción de tiempo real parece exigir funcionalidad mas desarrollada aún para pasar la funcionalidad de hipervisor de la software a la hardware.

También me parece muy interesante las informaciones sobre la vulnerabilidad con foco en sistemas embebidos. Un ejemplo para esto que quiero presentar es el peligro que representa el poder acceder el sistema final por JTAG por ejemplo! Trustzone y mentor Graphics artículos hablan de la necesidad de implementar la funcionalidad de autorización a nivel de la hardware con instrucciones especiales que entonces son responsables cuando una funcionalidad de la software requiere comunicarse con software en la zona segura, Trustzone! Evidente me parece el ejemplo que dan cuando un evento exterior, que pudiera venir de un atacante, ejecuta una interrupción de alta prioridad. Entonces la hardware del controlador tiene que resetar el contenido de registros de la trustzone para impedir así el ingresar del atacante. Una vez que la ejecución vuelve al código ejecutado en la zona de seguridad, entonces la hardware tiene que poner los valores originales en los registros reseteados!

El IoT, IIoT o Industria 4.0 en conjunto con los múltiples núcleos en controladores modernos y que estos sistemas están conectados a redes y por lo tanto susceptibles a ataques. Pero también las interacciones de programas actuando en paralelo en diferentes núcleos hacen el tema de la seguridad y la programación adecuada algo supremamente mas complejo!

Quiero publicando esta contribución compartir estas informaciones. Pero también ojala encontrar foristas que también tienen conocimientos sobre el tema! El hilo creo que está bién aquí, pues las placas Raspis, en especial la RaspBerry Pi 3B que tiene un controlador ARM con las instrucciones de la versión V8. Veo que la implementación de la estructura informática de mi taller me da la posibilidad de meterme en esta materia para luego ver y analizar si la placas Raspi 3B en su SoC ya apoya tales funcionalidades! Con seguridad el tema, que parece estar en auge desde algún tiempo bastante reciente, será apoyado por modernas placas Raspi, siendo la 3B la primera que debiera tenerla! Como la sofisticación del tema impactará las implementaciones futuras, vale empezar a familiarizarse con el tema hoy, si fuera de interés.

Tanto en mi PC, donde actualmente uso un i7 620, como con el Xenion X5550 a 2,67 GHz, uso procesadores con funcionalidad para operar hipervisor del tipo 1. Me compré 2 Xenion X5550 por solo 26,70 Euros incluyendo el costo del flete con LGA1366.

El hombrecito a la derecha abajo, yo y mi ordenador principalmente usa Windows 10, pero tengo un segundo disco duro con Ubuntu 16.04 TLS! Esto lo dejaré por ahora al menos, tal cual está. Ya estoy armándome el servidor con una placa madre ASUS P&t WS Professional a la cual le pondré unos de los procesadores Xenion 5550. Alí me voy a dedicar al reto de instalar el hipervisor tipo 1. Aún estoy investigando de que proveedor. Sobre el hipervisor pondré un entorno virtual con Windows 10 Pro y otra entorno virtual con Ubuntu 16.04 TLS.

Alguno de Ustedes ya tiene experiencias con hipervisores?

Por WiFi en el centro del gráfico ven las placas Raspi conectadas de forma inalámbrica con el servidor.

Aquí el enlace a un artículo muy interesante para mis objetivos y es que en controladores del tipo ARM Cortex basadas en la versión V8 la empresa ARM ha portado lo que llama Trustzone. Es funcionalidad de apoyo para la funcionalidad de hipervisor.

Voy a empezar a investigar cual proveedor ya es activo en este sector. las chances son muy buenas investigar en el entorno de los productos provenientes de Freescale en NXP. Esta es la parte del uso de la virtualización y el encapsulamiento lograble aislando partes de los programas en entornos virtuales proporcionados por estas funcionalidades.

Aquí un segundo artículo que consta de la "parte uno" y "la parte dos".

Esta serie de artículos a la que quiero sumar tales de la empresa "Mentor Graphics" se discute el tema de hipervisores como método de protección en sistemas embebidos con ejemplo a los entornos de sistemas embebidos en carros en general y de ciculación autónoma. Allí también cuentan que por ejemplo la industria de aviación ve en esta metodología una forma mas avanzada de proteger sus sistemas. Pero también las informaciones de la funcionalidad de hipervisores en sistemas embebidos, deep embedded, donde los tiempos de reacción de tiempo real parece exigir funcionalidad mas desarrollada aún para pasar la funcionalidad de hipervisor de la software a la hardware.

También me parece muy interesante las informaciones sobre la vulnerabilidad con foco en sistemas embebidos. Un ejemplo para esto que quiero presentar es el peligro que representa el poder acceder el sistema final por JTAG por ejemplo! Trustzone y mentor Graphics artículos hablan de la necesidad de implementar la funcionalidad de autorización a nivel de la hardware con instrucciones especiales que entonces son responsables cuando una funcionalidad de la software requiere comunicarse con software en la zona segura, Trustzone! Evidente me parece el ejemplo que dan cuando un evento exterior, que pudiera venir de un atacante, ejecuta una interrupción de alta prioridad. Entonces la hardware del controlador tiene que resetar el contenido de registros de la trustzone para impedir así el ingresar del atacante. Una vez que la ejecución vuelve al código ejecutado en la zona de seguridad, entonces la hardware tiene que poner los valores originales en los registros reseteados!

El IoT, IIoT o Industria 4.0 en conjunto con los múltiples núcleos en controladores modernos y que estos sistemas están conectados a redes y por lo tanto susceptibles a ataques. Pero también las interacciones de programas actuando en paralelo en diferentes núcleos hacen el tema de la seguridad y la programación adecuada algo supremamente mas complejo!

Quiero publicando esta contribución compartir estas informaciones. Pero también ojala encontrar foristas que también tienen conocimientos sobre el tema! El hilo creo que está bién aquí, pues las placas Raspis, en especial la RaspBerry Pi 3B que tiene un controlador ARM con las instrucciones de la versión V8. Veo que la implementación de la estructura informática de mi taller me da la posibilidad de meterme en esta materia para luego ver y analizar si la placas Raspi 3B en su SoC ya apoya tales funcionalidades! Con seguridad el tema, que parece estar en auge desde algún tiempo bastante reciente, será apoyado por modernas placas Raspi, siendo la 3B la primera que debiera tenerla! Como la sofisticación del tema impactará las implementaciones futuras, vale empezar a familiarizarse con el tema hoy, si fuera de interés.