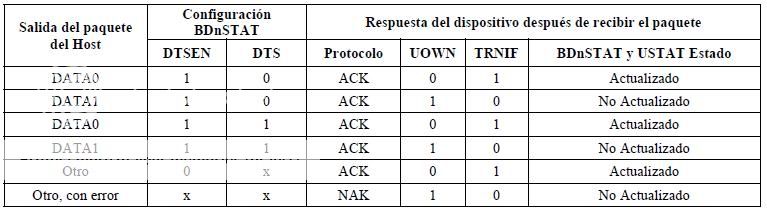

EFECTO DEL BIT DTSEN EN LA RECEPCIÓN DE PAQUETES PARES/IMPARES (DATA0/DATA1):

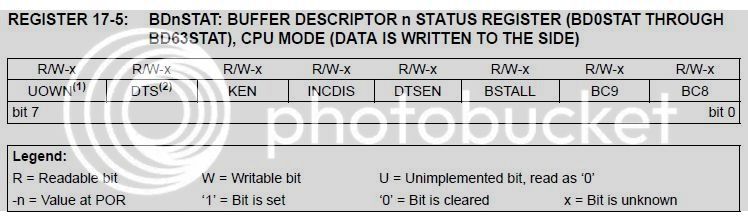

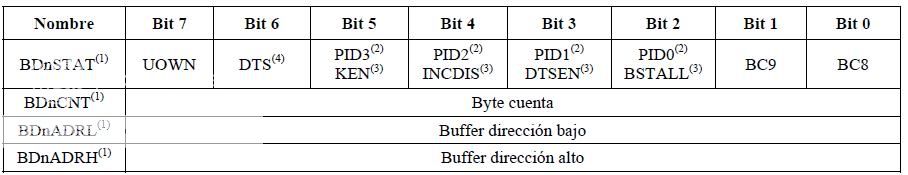

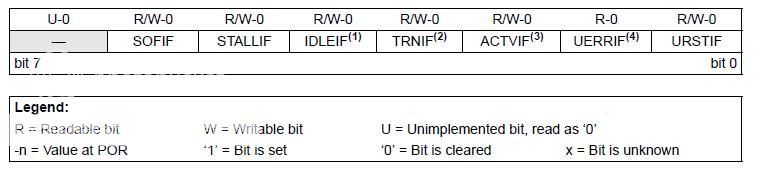

BDnSTAT: REGISTRO DEL ESTADO DEL BUFFER DESCRIPTOR n (BD0STAT HASTA BD63STAT), MODO CPU (LOS DATOS SE ESCRIBEN AL LADO):

BIT 7 UOWN: Bit de posesión del USB(1)

0 = El núcleo del microcontrolador posee el BD y su Buffer correspondiente.

BIT 6 DTS: Bit de sincronización de los datos(2)

1 = Paquete de datos 1.

0 = Paquete de datos 0.

BIT 5 KEN: Bit de permiso de la subsistencia de BD.

1 = USB guardará el BD indefinidamente una vez que UOWN se active

(requerido en la configuración de los Endpoint del SPP).

0 = USB guardará el último símbolo procesado.

BIT 4 INCDIS: Bit de inhabilitación del incremento de la dirección

1 = El incremento de la dirección inhabilitado (requerido en la configuración de los

Endpoint del SPP).

0 = Incremento de la dirección permitido.

BIT 3 DTSEN: Bit de permiso de la sincronización.

1 = Sincronización de los datos permitida; los paquetes de los datos con valor

incorrecto de la sinc. se ignoran excepto un SETUP, que se acepta.

0 = ninguna sincronización de los datos.

BIT 2 BSTALL: Bit de permiso de paradas en el Buffer.

1 = Parada del Buffer permitida; el protocolo de la STALL publica si se recibe un

símbolo que utilizaría el BD en la localización dada (UOWN se activa, el resto sin

cambios).

0 = parada del Buffer inhabilitado.

BIT 1-0 BC9:BC8: Bits del byte de cuenta 9 y 8.

Los bits de cuenta del byte representan el número de bytes que se transmitirán

con un símbolo IN o recibidos durante un símbolo OUT. Junto con BC<7:0>, las

cuentas de byte válidas son 0-1023.

Nota 1:Este bit debe inicializarlo el usuario con el valor deseado antes de permitir el módulo USB.

Nota 2:Se ignora este bit a menos que DTSEN = 1.

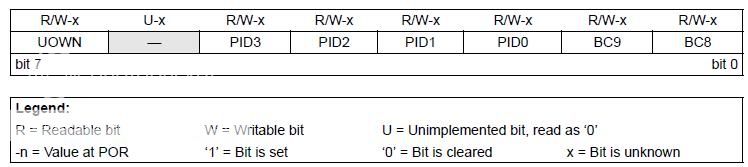

Registros BDnSTAT (modo SIE):

Cuando los BDs y su Buffer los gobierna el SIE, la mayoría de los bits de BDnSTAT toman distintos significados. Al activarse UOWN, cualquier dato o ajuste de control escritos por el usuario se sobrescriben con datos del SIE.

El registro BDnSTAT lo actualiza el SIE con el identificador del paquete (PID) se almacena en BDnSTAT<5:3>. Se actualiza la cuenta de la transferencia en el registro BDnCNT correspondiente. Los valores que desbordan el registro de 8 bits se transportan a los dos dígitos más significativos de la cuenta, almacenados en BDnSTAT<1:0>.

BDnSTAT: REGISTRO DE ESTADO DEL BUFFER DESCRIPTOR n (BD0STAT A BD63STAT), MODO SIE (DATOS DEVUELTOS POR EL LADO DEL MICROCONTROLADOR):

BIT 7 UOWN: Bit de posesión del USB.

1= El SIE gobierna el BD y el buffer correspondiente.

BIT 5-2 PID3 ID0:

ID0: Bits identificadores del paquete. El valor recibido del símbolo PID de la

última transferencia (sólo IN, OUT o SETUP).

BIT 1-0 BC9:BC8: Bits del byte de cuenta 9 y 8.

Esto bits los actualiza el SIE para reflejar al número de bytes recibidos en una

transferencia OUT y el número de bytes transmitidos en una IN.

BYTE DE CUENTA DE BD:

El byte de cuenta representa el número total de bytes que se transmitirán durante una IN. Después de la transferencia IN, el SIE devolverá el número de bytes enviados al anfitrión.

Para una transferencia OUT, el byte de cuenta representa número máximo de los bytes que se pueden recibir y almacenar en la RAM del USB. Después de una transferencia OUT, el SIE devolverá el número real de bytes recibidos. Si este número excede el byte de cuenta correspondiente, el paquete de datos se rechazará y se generará un protocolo de intercambio NAK. Cuando sucede esto, el byte de cuenta no se actualiza.

El byte de cuenta de 10 bits se distribuye sobre dos registros. Los 8 bits más bajos de la cuenta residen en el registro BDnCNT. Los dos altos en BDnSTAT<1:0>. Esto representa una gama válida para el byte de 0 a 1023.

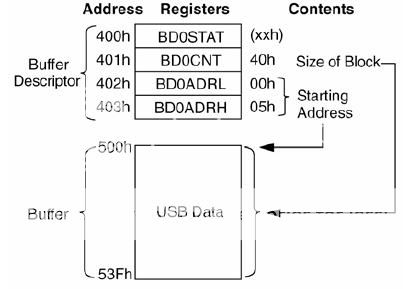

VALIDACIÓN DE LA DIRECCIÓN DE BD:

El par de registros de dirección de BD contiene la dirección de comienzo de la RAM para el Buffer del Endpoint correspondiente. Para que una localización que comienza en el Endpoint sea válida, debe estar en la gama de la RAM del USB, 400h a 7FFh. No hay ningún mecanismo por hardware para comprobar la dirección del BD.

Si el valor de la dirección de BD no señala a una dirección de la RAM del USB, o si señala a una dirección dentro del Buffer de otro Endpoint, es probable que se pierdan los datos o que se sobrescriban. Semejantemente, solapando un Buffer de recepción (Endpoint de salida) con una localización de BD en uso se obtienen resultados inesperados. Cuando se desarrollan aplicaciones USB, el usuario puede incluir software para validar las direcciones en el código.

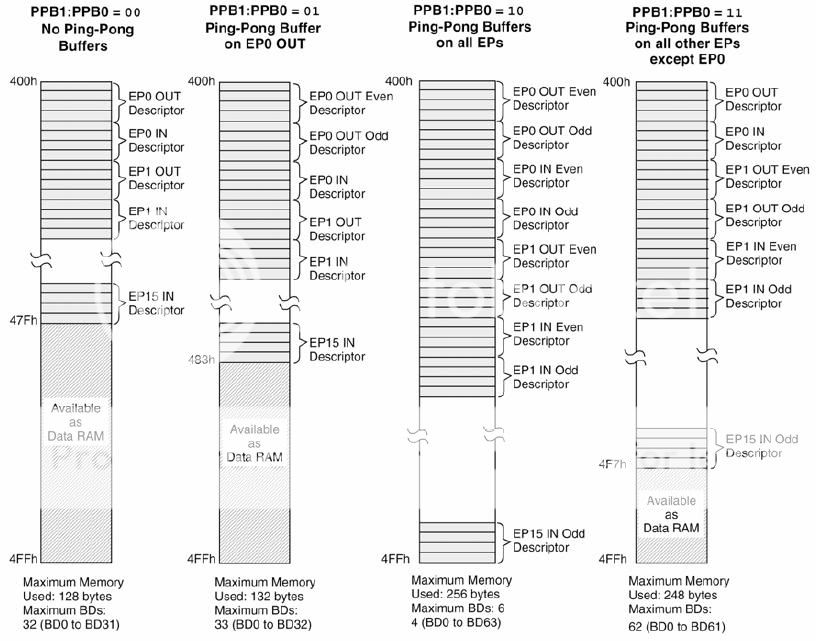

BUFFERING PING-PONG:

Un Endpoint se define para tener un Buffer ping-pong cuando tiene dos sistemas de entradas de BD: un sistema para una transferencia par y otro para una transferencia impar. Esto permite a la CPU procesar un BD mientras que el SIE procesa el otro BD.

El doble buffering BD, permite un rendimiento de procesamiento máximo del/al USB.

El módulo USB apoya cuatro modos de operación:

• Ninguna ayuda del ping-pong

• Ayuda del Buffer del ping-pong del OUT Endpoint 0 solamente

• Ayuda del Buffer del ping-pong para todas los Endpoints

• Ayuda del Buffer del ping-pong para el resto de los Endpoints excepto el 0

Los ajustes del Buffer ping-pong se configuran con los bits PPB1

PB0 en el registro UCFG.

El módulo USB no pierde de vista el puntero ping-pong de cada Endpoint.

Todos los punteros están reseteados inicialmente al BD par cuando se activa el módulo.

Al terminar una transacción (SIE borra UOWN), el puntero se une al BD impar. Al terminar la transacción siguiente, el puntero se une de nuevo al BD par y así sucesivamente.

El estado par/impar de la transacción realizada se almacena en el bit PBI del registro USTAT. El usuario puede resetear todos los punteros ping-pong al par con el bit PPBRST.

Cada BD tiene una relación fija con un Endpoint particular, dependiendo de la configuración del buffering. Esta relación significa también que pueden aparecer vacíos en las BDT si los Endpoints no se activan contiguamente. Esto significa en teoría, que los BDs de los Endpoints desactivados podían utilizarse como espacio de Buffer. En la práctica, los usuarios deben evitar usar tales espacios en el BDT a menos que el método de validar direcciones de BD esté en ejecución.

TABLAS DEL BUFFER DESCIPTOR MAPEADAS PARA LOS MODOS DE LOS BUFFER:

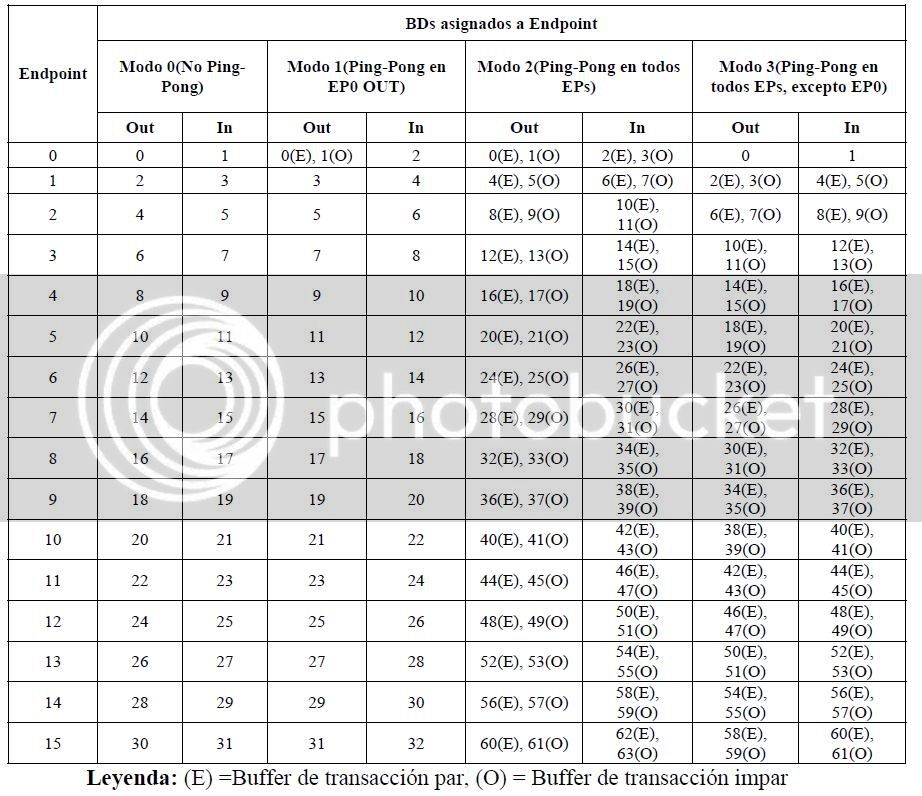

ASIGNACIÓN DE LOS BUFFERS DESCRIPTORES A LOS DIFERENTES MODOS DE BUFFERING: