La verdad, es un lindo diseño completamente simétrico... Hace mucho tiempo leí sobre el mismo. Mi mayor preocupación sería el posible embalamiento térmico por ser los 4 transistores de entrada independientes.

Variar la tensión base emisor de cualquiera, si no va compensado por otra variación igual del transistor siguiente, genera fluctuaciones en la corriente de operación de los transistores finales.

Para un clase A, posiblemente fuera aceptable, pero , bueno, me genera mis dudas la estabilidad a largo plazo del amplicador.

Por lo demás, es un diseño muy creativo e interesante

Justamente la estabilidad térmica es la que me da vueltas hace rato por la cabeza. Nunca armé uno totalmente simétrico y no tengo probado en la práctica para dónde puedan ir los corrimientos y qué tan importantes puedan ser.

Por el lado que estoy intentando ir es mantener a los transistores de baja señal bastante calientes, de modo que la variación de temperatura ambiente (por más que sea amplia) no tenga mucho impacto en los posibles corrimientos, después de estabilizada la temperatura normal de operación. Es decir, si mantengo temperaturas de operación de juntura de unos 75 grados, si la temperatura ambiente varía en 5 grados, el corrimiento va a ser 5/75 del punto de operación. En cambio, si la temperatura de operación de juntura es de 35 grados y si la temperatura ambiente varía en 5 grados, el corrimiento va a ser 5/35 del punto de operación. Puede que me equivoque, pero eso es lo que tengo planteado hacer hasta el momento.

Igual, tengo que masticarlo un poco más, todavía.

Por otro lado, confío en que los bajos valores resistivos del lazo de realimentación frenen cualquier posibilidad de corrimiento de la unión de emisores del par intermedio de transistores de baja señal. La intuición que tengo acerca de ese lazo conformado con muy bajos valores resistivos es que contemplando una situación límite de que esos valores tiendan a cero (manteniendo siempre la relación de 150 a 33), es que ambos emisores se van a mantener a un potencial más fijo que si esas resistencias tomaran valores mucho más importantes (como ser 150 K a 33 K). Intuyo que a los transistores intermedios les va a costar más desplazar el potencial de la unión de ambas resistencias del lazo (donde se conectan ambos emisores). Quizás me esté equivocando con mi intuición. Obviamente, habrá que otorgarle estabilidad térmica sobredimensionando adecuadamente la potencia de las resistencias de ese lazo. La analogía que podría plantear (aunque no la veo muy válida para este caso), para que me entiendas a lo que me refiero, es con un circuito bootstrap conformado con una capacidad por debajo del valor requerido (para los seguimientos de voltaje) y una red resistiva dura (de bajos valores resistivos): le va a terminar costando seguir las variaciones de voltaje en un amplio rango de frecuencias.

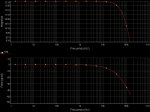

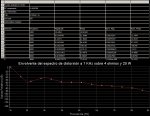

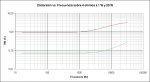

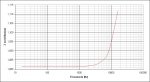

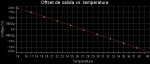

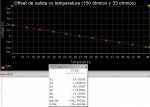

Aquí una simulación del offset de salida vs. temperatura ambiente:

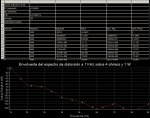

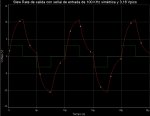

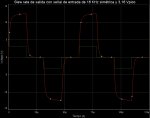

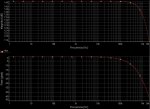

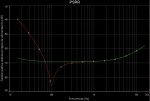

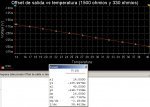

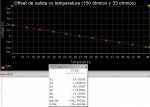

Luego, comparando entre dos variantes de resistencias en el lazo de realimentación:

Se puede ver que la ganancia en ambos casos es aprox. la misma. Más allá del desplazamiento del offset en los 27 grados que sufre la variante empleando resistencias más altas (lo cual es corregible), la variación dy/dx es mucho mayor que la otra variante, como yo intuía

. La diferencia es de casi 21,84 veces más de corrimiento en DC de la salida en la opción con resistencias de lazo 10 veces más grandes.

Saludos

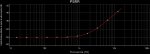

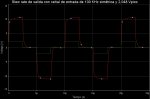

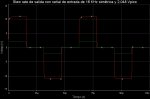

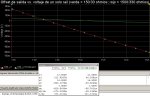

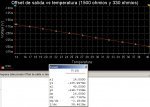

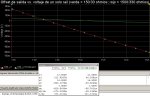

PD: en el fondo, le tengo un poco más de temor a la incidencia de una variación en el voltaje de alimentación (si se lo plantea no estabilizado) en la corriente de polarización general que a la incidencia que pueda tener en la misma una variación en la temperatura ambiente. Por burdos tanteos, da una variación de casi 277 mV por 3 voltios modificados (en la variante de 1500 ohmios y 330 ohmios) contra casi 10 veces menos (en la variante de 150 ohmios y 33 ohmios).

No he tenido tiempo de hacer la simulación con ambos rails variando, pero modificando uno solo ya nos da una idea para dónde puede ir la cosa. El rail que se ha modificado en las dos simulaciones es V1.

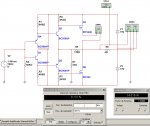

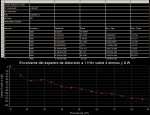

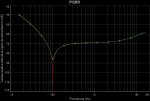

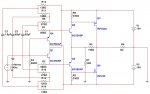

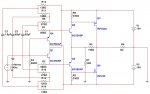

Finalmente, el circuito con el PSRR mejorado:

En realidad, deben hacer pequeños ajustes en torno a los valores resistivos desde donde se toman los condensadores de bypass, para que arrojen los niveles simulados. En el esquema se han dispuesto los valores normalizados más cercanos. Eso lo dejo para tarea de uds.

(no es cuestión de dar todo en bandeja

).

![2v9cgig[1].jpg 2v9cgig[1].jpg](https://www.forosdeelectronica.com/data/attachments/109/109800-9fb56e6dcde327eb04287867b9c5f56d.jpg)