Hola a todos! Estoy estudiando para rendir examen y me surgió una duda con respecto a memorias ROM que quisás alguna persona pueda aclararme. Se trata sobre el tamaño y la organización de una memoria ROM es decir en mi curso (que no se si es así en todos lados) un ejercicio común es construir una ROM a partir de otras ROM's dadas de memorias más chicas.

Por ejemplo un ejercicio me pide:

Se desea utilizar una ROM para implementar un comparador BCD (Decimal Empaquetado). El comparador recibe dos operandos representados en BCD de 8 bits cada uno y debe presentar a la salida el mayor de ellos representado en binario y un bit que indique cuál de los dos es el mayor (0 indica que el mayor es el operando presentado en la parte baja de la entrada ó que ambos son iguales y 1 indica que el mayor es el que está en la parte alta).

Se pide:

a) Determine el tamaño y la organización de la ROM de tamaño mínimo que permita resolver el problema planteado.

Construya dicha ROM. Para ello se dispone de compuertas básicas y las siguientes ROMs:

16K x 16 (se dispone de hasta 1 unidad)

16K x 8 (se dispone de hasta 1 unidad)

16K x 4 (se dispone de hasta 2 unidades)

64K x 1 (se dispone de hasta 1 unidad)

Entonces como primer paso se debe determinar el tamaño por letra se sabe que voy a disponer de dos operandos de 8 bits entonces tendría un tamaño de entrada de 16 bits como mínimo y luego necesitaría 8 bits de salida, un bit para ver indicar cuál es el mayor y 7 bits para representar el valor en binario de este ya que en BCD de 8 bits como máximo puedo representar el 99 y es representable con 7 bits. Hasta ahí va todo bien...mirando la solución dice algo así:

Por tanto se requiere la ROM mínima requerida es de 512 Kbits, organizada como 64 K palabras de 8 bits (64K x 8).

Esa primera parte no logro entenderla del todo, es decir se que si tengo una memoria A x B

se que la cantidad de entradas es [LATEX]\log_2A[/LATEX] y la cantidad de bits de salida es [LATEX]B[/LATEX] pero ¿de donde sale el 512 Kbits? es decir si a priori conozco la organización, por ejemplo 64k x 8 puedo conocer la cantidad de entradas y salidas.

Luego dice:

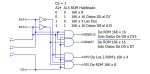

Para construir la ROM necesaria utilizamos la ROM de 16K x 16 disponible y formamos con ella una ROM de 32K x 8. Con las dos ROMs de 16K x 4 formamos una de 16K x 8, la que junto a la de 16K x 8 disponible formamos otra de 32K x 8. Con las dos de 32K x 8 que hemos construido se forma la de 64K x 8. Notar que no se requiere usar la ROM de 64K x 1.

¿Es correcto que piense que una memoria ROM de 16k x 16 sea equivalente a una de 32k x 8 porque son del mismo tamaño pero distintas organizaciones?

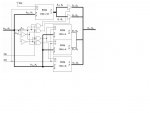

Por ultimo (disculpen por extenderme tanto) adjunto una imagen del circuito solución usando las ROM's antes mencionadas del cual no logro entender su funcionamiento, es decir que el circuito representa la ROM que se desea contruir pero me confunde porque en realidad las operaciones con los operandos en BCD no se ven en este, lo que se pide en la parte b) es un programa en alto nivel que cargue la ROM de forma adecuada pero en el circuito no se ve lo cual me resulta confuso y en si quería saber si alguien me puede explicar el uso de los OE(output enable) se que el CS(chip select) que está conectado a todos las ROM's directamente así que si este está en 0 entonces las salidas de las ROM's son 0 también pero no entiendo el OE porque distingue según las ROM's.

Saludos y gracias de antemano!

Por ejemplo un ejercicio me pide:

Se desea utilizar una ROM para implementar un comparador BCD (Decimal Empaquetado). El comparador recibe dos operandos representados en BCD de 8 bits cada uno y debe presentar a la salida el mayor de ellos representado en binario y un bit que indique cuál de los dos es el mayor (0 indica que el mayor es el operando presentado en la parte baja de la entrada ó que ambos son iguales y 1 indica que el mayor es el que está en la parte alta).

Se pide:

a) Determine el tamaño y la organización de la ROM de tamaño mínimo que permita resolver el problema planteado.

Construya dicha ROM. Para ello se dispone de compuertas básicas y las siguientes ROMs:

16K x 16 (se dispone de hasta 1 unidad)

16K x 8 (se dispone de hasta 1 unidad)

16K x 4 (se dispone de hasta 2 unidades)

64K x 1 (se dispone de hasta 1 unidad)

Entonces como primer paso se debe determinar el tamaño por letra se sabe que voy a disponer de dos operandos de 8 bits entonces tendría un tamaño de entrada de 16 bits como mínimo y luego necesitaría 8 bits de salida, un bit para ver indicar cuál es el mayor y 7 bits para representar el valor en binario de este ya que en BCD de 8 bits como máximo puedo representar el 99 y es representable con 7 bits. Hasta ahí va todo bien...mirando la solución dice algo así:

Por tanto se requiere la ROM mínima requerida es de 512 Kbits, organizada como 64 K palabras de 8 bits (64K x 8).

Esa primera parte no logro entenderla del todo, es decir se que si tengo una memoria A x B

se que la cantidad de entradas es [LATEX]\log_2A[/LATEX] y la cantidad de bits de salida es [LATEX]B[/LATEX] pero ¿de donde sale el 512 Kbits? es decir si a priori conozco la organización, por ejemplo 64k x 8 puedo conocer la cantidad de entradas y salidas.

Luego dice:

Para construir la ROM necesaria utilizamos la ROM de 16K x 16 disponible y formamos con ella una ROM de 32K x 8. Con las dos ROMs de 16K x 4 formamos una de 16K x 8, la que junto a la de 16K x 8 disponible formamos otra de 32K x 8. Con las dos de 32K x 8 que hemos construido se forma la de 64K x 8. Notar que no se requiere usar la ROM de 64K x 1.

¿Es correcto que piense que una memoria ROM de 16k x 16 sea equivalente a una de 32k x 8 porque son del mismo tamaño pero distintas organizaciones?

Por ultimo (disculpen por extenderme tanto) adjunto una imagen del circuito solución usando las ROM's antes mencionadas del cual no logro entender su funcionamiento, es decir que el circuito representa la ROM que se desea contruir pero me confunde porque en realidad las operaciones con los operandos en BCD no se ven en este, lo que se pide en la parte b) es un programa en alto nivel que cargue la ROM de forma adecuada pero en el circuito no se ve lo cual me resulta confuso y en si quería saber si alguien me puede explicar el uso de los OE(output enable) se que el CS(chip select) que está conectado a todos las ROM's directamente así que si este está en 0 entonces las salidas de las ROM's son 0 también pero no entiendo el OE porque distingue según las ROM's.

Saludos y gracias de antemano!