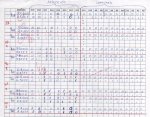

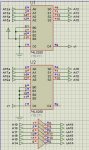

lo que pasa es que tengo que hacer el circuito con el decodificador y demás para el siguiente banco de memorias

se tienen eprom 32k*8, sram 16k*8 y eeprom 64k*8

<----8bits---->

_____________A5000h

| eeprom |

_____________

|64k sram |

_____________

|96k libre |

_____________

|128k eprom |

_____________

| 32k libre |

_____________25000h

ya hice el mapa ampliado, y lo veo bien, pero me da con un decodificador de 8 a 256bits con salidas de 4k (demasiado grande para dibujar) no se si estará bien, o si esta bien alguna manera de hacerlo con decodificadores mas pequeños, ayuda por favor! y gracias de antemano

se tienen eprom 32k*8, sram 16k*8 y eeprom 64k*8

<----8bits---->

_____________A5000h

| eeprom |

_____________

|64k sram |

_____________

|96k libre |

_____________

|128k eprom |

_____________

| 32k libre |

_____________25000h

ya hice el mapa ampliado, y lo veo bien, pero me da con un decodificador de 8 a 256bits con salidas de 4k (demasiado grande para dibujar) no se si estará bien, o si esta bien alguna manera de hacerlo con decodificadores mas pequeños, ayuda por favor! y gracias de antemano