Aqui les dejo el primer programa que he echo y probado en mi FPGA.

Es muy sencillo la idea es familiarizarse con el ISEweb pack.

Es muy sencillo la idea es familiarizarse con el ISEweb pack.

Código:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

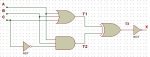

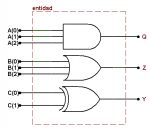

entity primero is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

SIGNAL C : out STD_LOGIC);

end primero;

architecture primero of primero is

begin

C <= A AND B;

end primero;

Última edición por un moderador: