ok, perfecto, no había caido en la resolución de mi osciloscopio, lo miro, aunque efectivamente no creo que "hile" tan fino, este es un osciloscopio normalito, no es un "pata negra".Ok , dices que la Norma especifica una precisión de mas o menos 80Hz maximos en 457KHz , tu oscilocopio tiene esa precisón en la medida ?

Creo que no , por eso necesitas de un frequenzimetro digital.

Att,

Daniel Lopes.

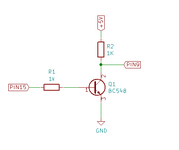

Perdona, no se si te habia contestado.Desde la respuesta 4 que di en el orden de este tema AQUI , el esquema esta claro para realizar una división de 14 mediante el 74LS161 pero al menos yo no lo veo en las fotos del protoboard armado ni en las simulaciones el inversor que debe llevar entre los pines 15 y 9.

Ver el archivo adjunto 261087

Tal vez me equivoque pero cuando así lo arme en el simulador aquí funciono perfectamente el factor de división.

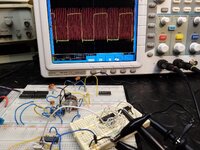

bueno, como quito, pongo........ en fin, en alguna de las pruebas si que lo he puesto, pero esta claro que en esta última nop?, así GRACIAS, por recordarmelo, voy al lio. ya cuento resultado.

Mensaje automáticamente combinado:

ufff...uf..... que cerca stoyyyyyyyyy........ creo que el unico inversor 74hc04 que tengo esta "petado" de ahí que en anteriorres pruebas,o consiguiese resultados, en su lugar he puesto (no se si valdrá), pero para muestra un botón, un 74ls14Desde la respuesta 4 que di en el orden de este tema AQUI , el esquema esta claro para realizar una división de 14 mediante el 74LS161 pero al menos yo no lo veo en las fotos del protoboard armado ni en las simulaciones el inversor que debe llevar entre los pines 15 y 9.

Ver el archivo adjunto 261087

Tal vez me equivoque pero cuando así lo arme en el simulador aquí funciono perfectamente el factor de división.

Mensaje automáticamente combinado:

he mandado el msj sin darme cuenta y no he incluido la imagen.

Última edición: